# Description

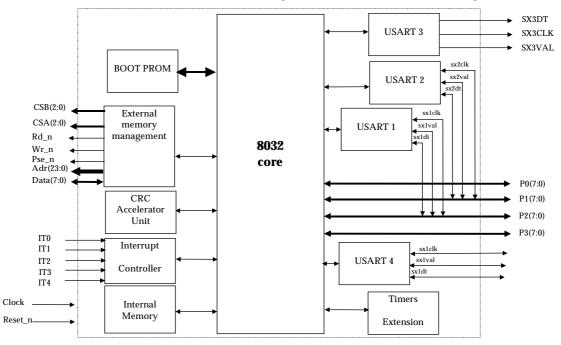

The 80S32 is a high performance microcontroller. It is fully compatible with the well-known 80C32/80C52 device and the technology combines high execution speed with high level of integration. Some features have been added to the 80C32 device and the performance has been increased by a factor of 3 that means a processing power of about 2.3 MIPS at 15 MHz. This device is powerful enough to handle the requirements of embedded on board applications.

# **Specific Features**

- 512 bytes on-chip memory;

- Full 64 Kbytes addressing range for program and data, with expansion up to 16 Mbytes for data and 8 Mbytes for program;

- De-multiplexed Address/Data bus ;

- Memory protection for both internal and external memory;

- Program downloading and program execution from RAM capabilities;

- Fives serial interfaces:

- \* One RS232 UART;

- \* Four extra configurable USARTs (RS232, PacketWire and TTC-B-01 compatible);

- \* two 64 bytes FIFO that can be associated to one of the extra USART and used as emission or reception buffer;

- Three 16-bit counters/timers with extended time count duration;

- Five external interrupts with two priority levels;

- A CRC calculation acceleration unit compatible with CCSDS TM and TC packets;

V 2.5 - 22/05/01

# **Table of contents**

| 1.                               | Intro               | troduction                                                               |    |  |  |  |

|----------------------------------|---------------------|--------------------------------------------------------------------------|----|--|--|--|

|                                  | 1.1                 | Scope                                                                    | .4 |  |  |  |

|                                  | 1.2                 | 1.2 Reference documents                                                  |    |  |  |  |

|                                  | 1.3                 | Convention                                                               |    |  |  |  |

| 2.                               |                     | cial Function registers                                                  |    |  |  |  |

|                                  | -                   |                                                                          |    |  |  |  |

|                                  | <b>2.1</b><br>2.1.1 | Original Special Function Registers<br>PSW: PROGRAM STATUS WORD REGISTER |    |  |  |  |

|                                  | 2.1.2               |                                                                          |    |  |  |  |

|                                  | 2.1.3               |                                                                          |    |  |  |  |

|                                  | 2.1.4               |                                                                          |    |  |  |  |

|                                  | 2.1.                |                                                                          |    |  |  |  |

|                                  | 2.1.0               |                                                                          |    |  |  |  |

|                                  | 2.1.                |                                                                          |    |  |  |  |

|                                  | 2.1.8               |                                                                          |    |  |  |  |

|                                  | 2.2                 | Additional Special Function Registers                                    |    |  |  |  |

|                                  |                     | -                                                                        |    |  |  |  |

| 3.                               | men                 | ory organization                                                         | 14 |  |  |  |

|                                  | 3.1                 | Introduction                                                             | 14 |  |  |  |

|                                  | 3.2                 | Internal Memory                                                          | 15 |  |  |  |

|                                  | 3.2.1               |                                                                          |    |  |  |  |

|                                  | 3.2.2               | 2 Upper 128 Bytes: Address $80_{\rm H}$ - FF <sub>H</sub>                | 16 |  |  |  |

| 3.2.3 Internal Memory protection |                     | 3 Internal Memory protection                                             | 17 |  |  |  |

|                                  | 3.3                 | eXtended RAM (XRAM)                                                      | 18 |  |  |  |

|                                  | 3.4                 | External memory                                                          | 19 |  |  |  |

|                                  | 3.4.                |                                                                          |    |  |  |  |

|                                  | 3.4.2               | 2 External memory access                                                 | 21 |  |  |  |

|                                  | 3.4.3               | 3 External Memory Protection                                             | 24 |  |  |  |

|                                  | 3.4.4               |                                                                          |    |  |  |  |

|                                  | 3.4.5               | 1                                                                        |    |  |  |  |

|                                  | 3.4.0               | 5 Memory organization summary                                            | 30 |  |  |  |

|                                  | 3.5                 | On chip bootstrap program                                                | 32 |  |  |  |

|                                  | 3.6                 | Error Detection and Correction (EDAC)                                    | 36 |  |  |  |

|                                  | 3.7                 | Special Function Register used for memory management                     | 37 |  |  |  |

| 4.                               | Tim                 | er/counters                                                              | 41 |  |  |  |

|                                  | 4.1                 | 8032 Timer operation summary                                             |    |  |  |  |

|                                  | 4.1.1               |                                                                          |    |  |  |  |

|                                  | 4.1.2               |                                                                          |    |  |  |  |

|                                  | 4.1.3               | C C                                                                      |    |  |  |  |

V 2.5 - 22/05/01

| 5.1   | Introduction                                                                                       |                             |  |

|-------|----------------------------------------------------------------------------------------------------|-----------------------------|--|

| 5.2   | Configuration4                                                                                     |                             |  |

|       | <b>RS232 asynchronous type mode</b>                                                                |                             |  |

|       | Synchronous Packet Wire mode           .4.1         Reception.           .4.2         Transmission |                             |  |

|       | Synchronous TTC-B-01 mode           .5.1         Transmission           .5.2         Reception     |                             |  |

| 5.6   | Transmission and reception FIFOs                                                                   |                             |  |

| 6. In | nterrupt controller                                                                                |                             |  |

| 7. Cl | RC accelerator unit                                                                                |                             |  |

| 8. I/ | O ports                                                                                            |                             |  |

| 9. In | nterface and signal description                                                                    |                             |  |

| 9.1   | Interface signals                                                                                  |                             |  |

| 9.2   | Alternative port functions                                                                         |                             |  |

| 10.   | ADV 80S32 Instruction List                                                                         |                             |  |

| 10.1  | Key to addressing modes                                                                            |                             |  |

| 10.2  | 2 Arithmetic Operations                                                                            |                             |  |

| 10.3  | 3 Logical Instructions                                                                             |                             |  |

| 10.4  | 1 Data Transfer                                                                                    |                             |  |

| 10.5  | 5 Boolean Variable Manipulation                                                                    |                             |  |

| 10.6  | 6 Program Branching                                                                                |                             |  |

| 10.7  | 7 Performance Comparison                                                                           |                             |  |

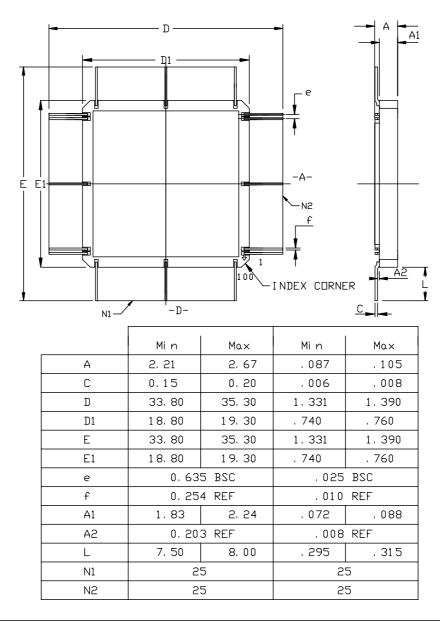

| 11.   | Electrical and mechanical data                                                                     | Erreur ! Signet non défini. |  |

| 11.1  | Absolute maximum ratings                                                                           | Erreur ! Signet non défini. |  |

| 11.2  | 2 DC specifications                                                                                | Erreur ! Signet non défini. |  |

| 11.3  | 3 AC specifications                                                                                | Erreur ! Signet non défini. |  |

# 1. INTRODUCTION

#### 1.1 Scope

This data sheet presents the technical information concerning the ADV 80S32 microcontroller which is an 8-bit microcontroller based on the well-known 8052/51 device and improved for space application.

The 80S32 microcontroller is 100% code compatible with the original 8052/51 and provides the following extra features:

- 256 bytes of additional on-chip memory;

- On-chip EDAC protecting external and internal memory;

- 4 extra USARTs supporting RS232, Packet Wire and TTC-B-01 protocols;

- Extended interrupt control capabilities with 5 instead of 2 external interrupts;

- CRC accelerator unit processing 8 bit calculation in 2 clock cycles;

- Extension of the time duration of the 3 counters;

- Program downloading capabilities via PacketWire interface;

This data sheet only contains the description of all the specific features of the 80S32 microcontroller and is not duplicating generic information on the 8052/51 that is available in public documentation. RD1 is the reference document that has been used during the development.

#### **1.2 Reference documents**

- **RD-1** 'MCS51 MICROCONTROLLER FAMILY USER'S MANUAL' INTEL (can be downloaded from http://developper.intel.com/design/mcs51/manuals).

- RD-2 Packet Telecommand Decoder (PTD) Data Sheet, MA28140, GPS SOS Radiation Hard Handbook, July 1994,

- RD-3 Telecommand Decoder Specification, ESA PSS-04-151, Issue 1, September 1993

- **RD-4** Virtual Channel Assembler (VCA) Preliminary Data Sheet, MS12399, Mitel Semiconductor, January 1994

- RD-5 Spacecraft data Handling Interface Standards TTC-B-01, Issue 1, September 1979

#### **1.3 Convention**

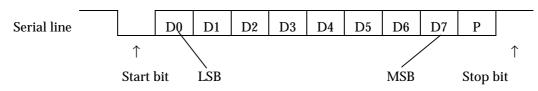

The following convention to present byte data is used in this document:

|      | MSB |         |       |    |    |        |        | LSB |

|------|-----|---------|-------|----|----|--------|--------|-----|

| Byte | 7   | 6       | 5     | 4  | 3  | 2      | 1      | 0   |

|      | Up  | per nil | ble M | SN | Lo | wer ni | bble L | SN  |

# 2. SPECIAL FUNCTION REGISTERS

All the special function registers of the original 8051/52 are present in the 80S32 device and are repeated in §2.1. Extra SFRs have also been added for the implementation of the new functions and are presented in §2.2.

# 2.1 Original Special Function Registers

All the special function registers of the original 8051/52 are present in the ADV 80S32 devices. More detailed information on their use can be obtained from an 805x data sheet.

| SFR    | Function                         | Address                       | Reset Value                |

|--------|----------------------------------|-------------------------------|----------------------------|

| ACC    | Accumulator                      | E0 <sub>H</sub>               | 00                         |

| В      | B Register                       | F0 <sub>H</sub>               | 00                         |

| PSW    | Program Status Word              | D0 <sub>H</sub>               | 00                         |

| SP     | Stack Pointer                    | 81 <sub>H</sub>               | 07 <sub>н</sub>            |

| DPL    | Data Pointer low byte            | 82 <sub>H</sub>               | 00                         |

| DPH    | Data Pointer high byte           | 83 <sub>H</sub>               | 00                         |

| P0     | Port0                            | 80 <sub>H</sub>               | $\mathbf{FF}_{\mathrm{H}}$ |

| P1     | Port1                            | 90 <sub>H</sub>               | $\mathbf{FF}_{\mathrm{H}}$ |

| P2     | Port2                            | A0 <sub>H</sub>               | $\mathbf{FF}_{H}$          |

| P3     | Port3                            | B0 <sub>H</sub>               | $\mathbf{FF}_{\mathrm{H}}$ |

| IP     | Interrupt Priority Control       | $\mathbf{B8}_{_{\mathrm{H}}}$ | 00                         |

| IE     | Interrupt Enable Control         | A8 <sub>H</sub>               | 00                         |

| TMOD   | Timer/Counter Mode Control       | 89 <sub>H</sub>               | 00                         |

| TCON   | Timer/Counter Control            | 88 <sub>H</sub>               | 00                         |

| T2CON  | Timer/Counter 2 Control          | C8 <sub>H</sub>               | 00                         |

| TH0    | Timer/Counter 0 High Byte        | 8C <sub>H</sub>               | 00                         |

| TL0    | Timer/Counter 0 Low Byte         | 8A <sub>H</sub>               | 00                         |

| TH1    | Timer/Counter 1 High Byte        | $8D_{_{\rm H}}$               | 00                         |

| TL1    | Timer/Counter 1 Low Byte         | $\mathbf{8B}_{\mathrm{H}}$    | 00                         |

| TH2    | Timer/Counter 2 High Byte        | $\mathrm{CD}_{_{\mathrm{H}}}$ | 00                         |

| TL2    | Timer/Counter 2 Low Byte         | $\mathrm{CC}_{\mathrm{H}}$    | 00                         |

| RCAP2H | T/C 2 Capture Register High Byte | CB <sub>H</sub>               | 00                         |

| RCAP2L | T/C 2 Capture Register Low Byte  | CA <sub>H</sub>               | 00                         |

| SCON   | Serial Control                   | 98 <sub>H</sub>               | 00                         |

| SBUF   | Serial Data Buffer               | 99 <sub>H</sub>               | 00                         |

| PCON   | Power Control                    | 87 <sub>н</sub>               | 00                         |

|        |                                  |                               |                            |

**ADV Engineering** From Concepts to Products

## 2.1.1 PSW: PROGRAM STATUS WORD REGISTER

| <u>Bit</u> | Name | Description                                                   |

|------------|------|---------------------------------------------------------------|

| 7          | СҮ   | Carry flag                                                    |

| 6          | AC   | Auxiliary Carry flag                                          |

| 5          | F0   | General purpose status flag.                                  |

| 4          | RS1  | Register bank select bit 1                                    |

| 3          | RS0  | Register bank select bit 0                                    |

| 2          | OV   | Overflow flag                                                 |

| 1          | -    | User definable flag                                           |

| 0          | Р    | Parity flag. Set when there are an odd number of bits in ACC. |

| <u>RS1</u> | RS0 | Register Bank | Address                            |

|------------|-----|---------------|------------------------------------|

| 0          | 0   | 0             | 00 <sub>11</sub> -07 <sub>11</sub> |

| 0          | 1   | 1             | 08 <sub>H</sub> -0F <sub>H</sub>   |

| 1          | 0   | 2             | $10_{H}^{H} - 17_{H}^{H}$          |

| 1          | 1   | 3             | $18_{H}^{H} - 1F_{H}^{H}$          |

|            |     |               |                                    |

# 2.1.2 PCON: POWER CONTROL REGISTER

| <u>Bit</u> | Name | Description                                                                                                       |  |  |  |

|------------|------|-------------------------------------------------------------------------------------------------------------------|--|--|--|

| 7          | SMOD | Doubles the baud rate when set in serial mode 2 or when Timer1 is used to generate the baud rate in modes 1 or 3. |  |  |  |

| 3          | GF1  | General-purpose flag bit.                                                                                         |  |  |  |

| 2          | GF0  | General-purpose flag bit.                                                                                         |  |  |  |

| 1          | PD   | Set to enter power down mode.                                                                                     |  |  |  |

| 0          | IDL  | Set to enter idle mode.                                                                                           |  |  |  |

| NIOT       |      |                                                                                                                   |  |  |  |

NOTE: PD takes precedence over IDL.

### 2.1.3 IE: INTERRUPT ENABLE REGISTER

| Bit | Name | Description                                      |

|-----|------|--------------------------------------------------|

| 7   | EA   | Clear to globally disable all interrupt sources. |

| 5   | ET2  | Set to enable Timer2 interrupt.                  |

| 4   | ES   | Set to enable the Serial port interrupt          |

| 3   | ET1  | Set to enable Timer1 interrupt.                  |

| 2   | EX1  | Set to enable External interrupt1.               |

| 1   | ET0  | Set to enable Timer0 interrupt.                  |

| 0   | EX0  | Set to enable External interrupt0.               |

## 2.1.4 IP: INTERRUPT PRIORITY REGISTER

| Bit | Name | Description                          |

|-----|------|--------------------------------------|

| 5   | PT2  | Timer2 interrupt priority level      |

| 4   | PS   | Serial Port interrupt priority level |

| 3   | PT1  | Timer1 interrupt priority level      |

| 2   | PX1  | External interrupt 1 priority level  |

| 1   | PT0  | Timer0 interrupt priority level      |

| 0   | PX0  | External interrupt priority level    |

Priority levels are (from high to low):

IE0 TF0 IE1 TF1 RI or TI TF2 or EXF2

# 2.1.5 TCON: TIMER/COUNTER CONTROL REGISTER

| Bit | Name | Description                                                      |

|-----|------|------------------------------------------------------------------|

| 7   | TF1  | Timer1 overflow flag. Hardware controlled. Set when              |

|     |      | Timer/Counter1 overflows. Cleared when processor vectors to      |

|     |      | interrupt service routine.                                       |

| 6   | TR1  | When set, starts Timer/Counter1 running.                         |

| 5   | TF0  | Timer0 overflow flag. Hardware controlled. Set when              |

|     |      | Timer/Counter0 overflows. Cleared when processor vectors to      |

|     |      | interrupt service routine.                                       |

| 4   | TR0  | When set, starts Timer/Counter0 running.                         |

| 3   | IE1  | Set when External Interrupt1 detected. Cleared when interrupt is |

|     |      | processed. Hardware controlled.                                  |

| 2   | IT1  | Set to specify External Interrupt1 as falling edge triggered.    |

|     |      | Clear to specify External Interrupt1 as low level triggered.     |

| 1   | IE0  | Set when External Interrupt0 detected. Cleared when interrupt is |

|     |      | processed. Hardware controlled.                                  |

| 0   | IT0  | Set to specify External Interrupt0 as falling edge triggered.    |

|     |      | Clear to specify External Interrupt0 as low level triggered.     |

|     |      |                                                                  |

**ADV Engineering** *From Concepts to Products*

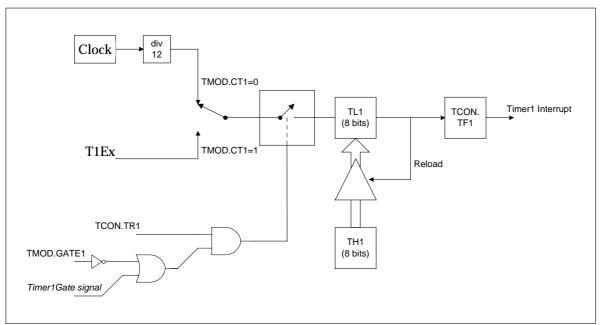

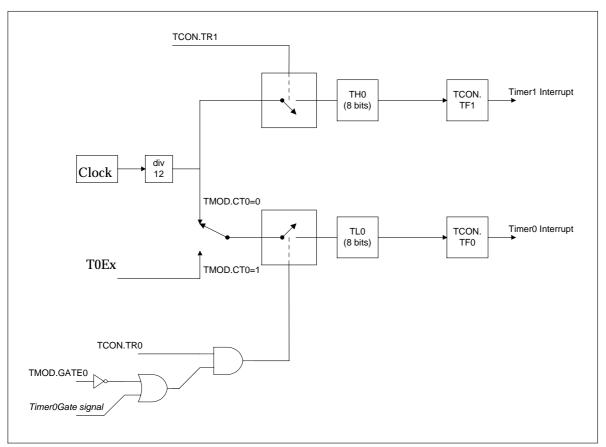

# 2.1.6 TMOD: TIMER/COUNTER MODE CONTROL REGISTER

| <u>Bit</u>  | Name          | Description                                                             |

|-------------|---------------|-------------------------------------------------------------------------|

| 7           | GATE1         | Set to specify Timer/Counter1 is gated when <i>Timer0Gate</i> =1.       |

| 6           | CT1           | Set to specify Timer/Counter1 as a counter (counting <i>Timer1</i> =1). |

|             |               | Clear to specify input from internal clock.                             |

| 5           | T1M1          | Timer/Counter1 mode select bit 1.                                       |

| 4           | T1M0          | Timer/Counter1 mode select bit 0.                                       |

| 3           | GATE0         | Set to specify Timer/Counter0 is gated when <i>Timer1Gate</i> =1.       |

| 2           | CT0           | Set to specify Timer/Counter0 as a counter (counting <i>Timer0</i> =1). |

|             |               | Clear to specify input from internal clock.                             |

| 1           | T0M1          | Timer/Counter0 mode select bit 1.                                       |

| 0           | T0M0          | Timer/Counter0 mode select bit 0.                                       |

|             |               |                                                                         |

| <b>TO</b> 1 |               |                                                                         |

| <u>10M</u>  | <u>1 T0M0</u> | Mode Operation                                                          |

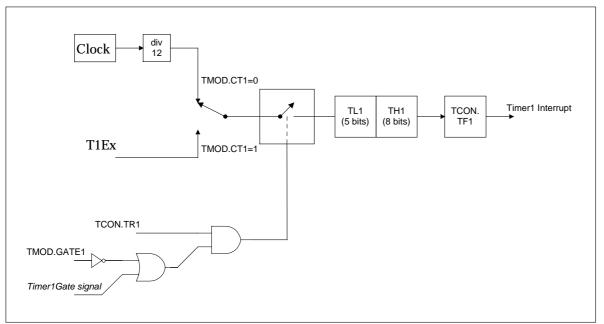

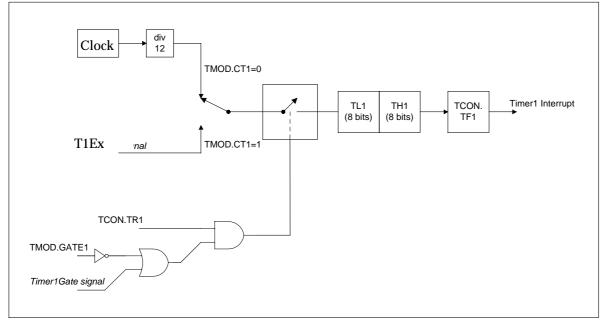

| 0           | 0             | 0 13-bit timer/counter                                                  |

| 0           | 1             | 1 16-bit timer/counter                                                  |

| 1           | 0             | 2 8-bit auto-reload timer/counter                                       |

| 1           | 1             | 3 TL0 is an 8-bit timer/counter controlled by the standard              |

|             |               | Timer0 control bits. TH0 is an 8-bit timer controlled by                |

|             |               | Timer1 control bits. Timer 1 is stopped.                                |

| T1M         | 1 T1M0        | Mode Operation                                                          |

| 0           | 0             | 0 13-bit timer/counter                                                  |

| 0           | 1             | 1 16-bit timer/counter                                                  |

| 1           | 0             | 2 8-bit auto-reload timer/counter                                       |

| 1           | 1             | 3 Timer1 is stopped.                                                    |

| -           | -             |                                                                         |

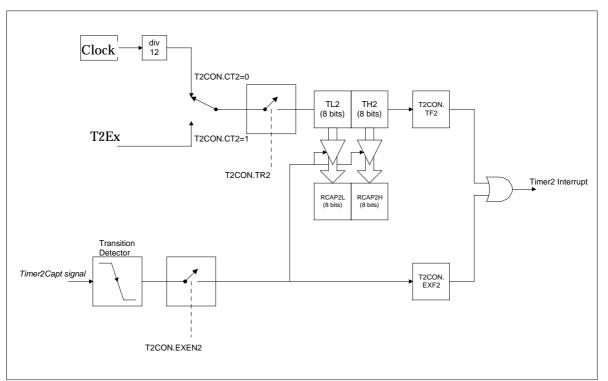

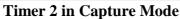

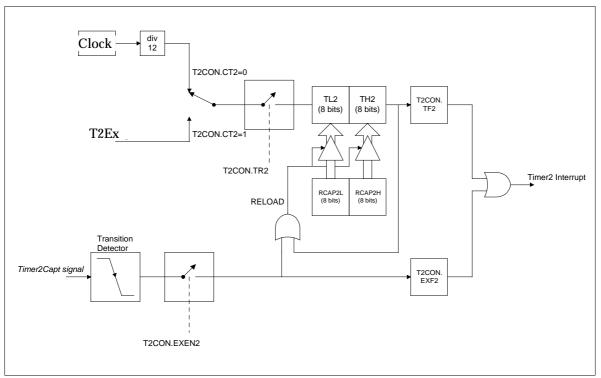

# 2.1.7 T2CON: TIMER/COUNTER 2 CONTROL REGISTER

| Bit | Name  | Description                                                                                                                                                                                                         |

|-----|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | TF2   | Set by hardware when Timer2 overflows, cleared by software.                                                                                                                                                         |

|     |       | Is not set when either RCLK=1 or TCLK=1.                                                                                                                                                                            |

| 6   | EXF2  | Timer2 External interrupt flag. Set whenever EXEN2=1 and a negative transition on <i>Timer2Capt</i> occurs. Causing a reload or capture, and a vector to the Timer2 interrupt service routine. Cleared by software. |

| 5   | RCLK  | When set, the serial port uses Timer2 overflows for its receive clock, otherwise it uses Timer1 overflows.                                                                                                          |

| 4   | TCLK  | When set, the serial port uses Timer2 overflows for its transmit clock, otherwise it uses Timer1 overflows.                                                                                                         |

| 3   | EXEN2 | When set allows a capture or reload to occur because of a negative transition on <i>Timer2Capt</i> , if Timer2 is not being used to clock the serial port (i.e. RCLK=0 and TCLK=0).                                 |

| 2   | TR2   | Set to start Timer2 running.                                                                                                                                                                                        |

| 1   | CT2   | Set to select Timer2 as falling edge triggered External Event Counter.                                                                                                                                              |

| 0   | CPRL2 | When set, Timer2 captures if EXEN2=1. When cleared, auto-reloads occur. If Timer2 is used to generate, the serial clock Timer2 is forced to auto-reload.                                                            |

| Mode                  | CPRL | 2 TCLK | RCLK | Comment                        |

|-----------------------|------|--------|------|--------------------------------|

| Capture               | 1    | 0      | 0    |                                |

| Auto Reload           | 0    | 0      | 0    |                                |

| Baud Generator        | Х    | 1      | 1    | receive and transmit same Baud |

| <b>Baud Generator</b> | Х    | 0      | 1    | set receive Baud only          |

| Baud Generator        | Х    | 1      | 0    | set transmit Baud only         |

'X' denotes don't care.

# 2.1.8 SCON: SERIAL PORT CONTROL REGISTER

| Bit | Name | Description                                                                                                                      |

|-----|------|----------------------------------------------------------------------------------------------------------------------------------|

| 7   | SM0  | Serial port mode bit 0                                                                                                           |

| 6   | SM1  | Serial port mode bit 1                                                                                                           |

| 5   | SM2  | If set in serial modes 2 or 3, RI is only activated if the 9th received                                                          |

|     |      | data bit (RB8) is 1. If set in serial mode 1, then RI is only activated                                                          |

|     |      | if a valid stop bit is received.                                                                                                 |

| 4   | REN  | Set to enable serial reception.                                                                                                  |

| 3   | TB8  | In serial modes 2 and 3, the 9th data bit transmitted.                                                                           |

| 2   | RB8  | In serial modes 2 and 3, the 9th data bit received.                                                                              |

| 1   | TI   | Transmit interrupt flag, set at the beginning of the stop bit, or at the end of the 8th bit time in mode 0. Cleared by software. |

| 0   | RI   | Receive interrupt flag, set halfway through the stop bit, or at the end of the 8th bit time in mode 0. Cleared by software.      |

| <u>SM0</u> | SM1 | Serial Mode | Description    | Baud Rate            |

|------------|-----|-------------|----------------|----------------------|

| 0          | 0   | 0           | Shift Register | Clock/12             |

| 0          | 1   | 1           | 8-bit UART     | Variable             |

| 1          | 0   | 2           | 9-bit UART     | Clock/64 or Clock/32 |

| 1          | 1   | 3           | 9-bit UART     | Variable             |

# 2.2 Additional Special Function Registers

To support the additional functions of the 80S32 the following registers have been added to the SFR space at locations that are not used in the original 8052/51 device.

| SYMBOL  | DESCRIPTION                                              | DIRECT<br>ADDR | BIT ADDRESS, SYMBOL, OR ALTERNATIVE PORT FUNCTION |            |         |         |            |         | ION     | ACCESS  |     |

|---------|----------------------------------------------------------|----------------|---------------------------------------------------|------------|---------|---------|------------|---------|---------|---------|-----|

|         |                                                          | (Hex)          | MSB                                               |            |         |         |            |         |         | LSB     |     |

| DTBANK  | Data memory bank                                         | 84             |                                                   |            |         | 8-bi    | t word     |         |         |         | R/W |

| PGBANK  | Program memory bank                                      | 85             | 0                                                 |            |         |         | 7-bit word | I       |         |         | R/W |

| DPSEL   | Data Pointer Select                                      | 92             | -                                                 |            |         |         |            |         |         | DPSEL   | R/W |

| SYSCON  | XRAM configuration                                       | 93             | -                                                 | -          |         | -       |            | -       | x       | MAP     | R/W |

| MPCON   | Internal memory protection configuration                 | 94             |                                                   |            |         |         | IPC        | CON     | XF      | PCON    | R/W |

| MPSTAT  | Internal and external memory protection status           | 95             | PG_ER                                             | _FLAG0     | DT_ER   | _FLAG1  | XM         | IER     | n       | MER     | R/W |

| EMCON   | External memory protection configuration                 | 96             | -                                                 | -          | PMO     | CON0    | DM         | CON     | F       | EMA     | R/W |

| CSCON   | CS configuration                                         | 9E             | -                                                 | -          | CSPG    | CON0    |            | -       | CSE     | DTCON   | R/W |

| IXERAD  | Internal memory error<br>address (LSB)                   | 9A             |                                                   |            |         | 8-bi    | t word     |         |         |         | R/W |

| PDERADL | External (program/data)<br>memory error address (LSB)    | A1             |                                                   | 8-bit word |         |         |            |         |         | R/W     |     |

| PDERADH | External (program/data)<br>memory error address (MSB)    | A2             | 8-bit word                                        |            |         |         |            | R/W     |         |         |     |

| P0DIR   | Port 0 direction control bits                            | A4             | 8-bit word                                        |            |         |         |            |         | R/W     |         |     |

| P1DIR   | Port 1 direction control bits                            | A5             | 8-bit word                                        |            |         |         |            | R/W     |         |         |     |

| P2DIR   | Port 2 direction control bits                            | A6             |                                                   | 8-bit word |         |         |            |         | R/W     |         |     |

| P3DIR   | Port 3 direction control bits                            | A7             |                                                   |            |         | 8-bi    | t word     |         |         |         | R/W |

| CRCIN   | CRC calculation input                                    | A9             |                                                   |            |         | 8-bi    | t word     |         |         |         | R/W |

| CRCL    | CRC calculation result and initialization register (LSB) | AA             |                                                   |            |         | 8-bi    | t word     |         |         |         | R/W |

| CRCH    | CRC calculation result and initialization register (MSB) | AB             |                                                   |            | 1       | 8-bi    | t word     |         | 1       |         | R/W |

| IXEP1   | Interrupt enable + priority<br>register 1                | AC             |                                                   | -          |         | -       | EE         | ХМ      | E       | INM     | R/W |

| IXEP2   | Interrupt enable + priority<br>register 2                | AD             | ES                                                | SX1        | ES      | SX2     | ES         | X3      | E       | 2SX4    | R/W |

| IXEP3   | Interrupt enable + priority<br>register 3                | AE             |                                                   | -          | E       | X4      | E          | X3      | 1       | EX2     | R/W |

| TDIVCON | Timer input selection                                    | B1             | TDI                                               | VIN        | Т       | IN      | T1         | IN      | Т       | 2IN     | R/W |

| TDIVL   | Timer input frequency division ratio (LSB)               | B2             | 8-bit word                                        |            |         |         |            | R/W     |         |         |     |

| TDIVH   | Timer input frequency division ratio (MSB)               | B3             |                                                   | 1          | 1       | 8-bi    | t word     | 1       | 1       | 1       | R/W |

| EXTBUS  | Address bus extension configuratiobon                    | В5             | EXTAD23                                           | EXTAD22    | EXTAD21 | EXTAD20 | EXTAD19    | EXTAD18 | EXTAD17 | EXTAD16 | R/W |

ADV Engineering, Parc technologique du canal, 16 avenue de l'Europe, 31520 Ramonville Saint Agne (France)

V 2.5 - 22/05/01

| SYMBOL   | DESCRIPTION                                        | DIRECT<br>ADDR |            |            |       |        |        | <b>RT FUNCTION</b> | ACCESS |      |

|----------|----------------------------------------------------|----------------|------------|------------|-------|--------|--------|--------------------|--------|------|

|          |                                                    | (Hex)          | MSB        |            |       |        |        |                    | LSB    |      |

| WAITMEM  | WAIT states configuration                          | 0C3            |            | ws         | PA    |        |        | W                  | SDA    | R/W* |

| P1CON    | Port 1 configuration bits                          | D8             |            |            |       | 8-bi   | t word |                    |        | R/W* |

| P2CON    | Port 2 configuration bits                          | E8             |            |            |       | 8-bi   | t word |                    |        | R/W* |

| P3CON    | Port 3 configuration bits                          | F8             |            |            |       | 8-bi   | t word |                    |        | R/W* |

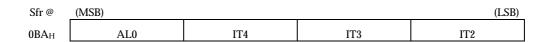

| TXCON1   | External interrupt control                         | BA             |            | -          | 1     | E4     | IE3    | 1                  | IE2    | R/W  |

| TXCON2   | External interrupt control                         | BB             | А          | L4         | ŀ     | AL3    | AL     | 2                  | AL1    | R/W  |

| TXCON3   | External interrupt control                         | BC             | А          | LO         | 1     | T4     | IT3    | 1                  | IT2    | R/W  |

| FIFOCON  | FIFO configuration                                 | C7             |            | TF         | IFO   |        |        | F                  | RFIFO  | R/W  |

| SX1CON1  | Extra USART1 configuration 1                       | D2             | MODE1      | MODE0      | ME2   | ME1    | ME0    |                    |        | R/W  |

| SX1CON2  | Extra USART1 configuration 2                       | D3             |            |            | RB8/E | OR/BOT | TI     |                    | RI     | R/W  |

| SX1BUFL  | Extra USART1<br>receive/transmit register<br>(LSB) | D4             |            | 1          | 1     | 8-bi   | t word |                    |        | R/W  |

| SX1BUFH  | Extra USART1<br>receive/transmit register<br>(MSB) | D5             |            |            |       | 8-bi   | t word |                    |        | R/W  |

| SX1FREQL | Extra USART1 frequency divider ratio (LSB)         | D6             |            | 8-bit word |       |        |        |                    |        | R/W  |

| SX1FREQH | Extra USART1 frequency divider ratio (MSB)         | D7             | 8-bit word |            |       |        |        | R/W                |        |      |

| SX2CON1  | Extra USART2 configuration 1                       | D9             | MODE1      | MODE0      | ME2   | ME1    | ME0    |                    |        | R/W  |

| SX2CON2  | Extra USART2 configuration 2                       | DA             |            |            | RB8/E | OR/BOT | TI     |                    | RI     | R/W  |

| SX2BUFL  | Extra USART2<br>receive/transmit register<br>(LSB) | DB             | 8-bit word |            |       |        |        |                    | R/W    |      |

| SX2BUFH  | Extra USART2<br>receive/transmit register<br>(MSB) | DC             |            |            |       | 8-bi   | t word |                    |        | R/W  |

| SX2FREQL | Extra USART2 frequency divider ratio (LSB)         | DD             |            |            |       | 8-bi   | t word |                    |        | R/W  |

| SX2FREQH | Extra USART2 frequency divider ratio (MSB)         | DE             |            |            |       | 8-bi   | t word |                    |        | R/W  |

| SX3CON1  | Extra USART3 configuration 1                       | E2             | MODE1      | MODE0      | ME2   | ME1    | ME0    |                    | -      | R/W  |

| SX3CON2  | Extra USART3 configuration 2                       | E3             |            |            | RB8/E | OR/BOT | TI     |                    | RI     | R/W  |

| SX3BUFL  | Extra USART3<br>receive/transmit register<br>(LSB) | E4             |            | 8-bit word |       |        |        |                    | R/W    |      |

| SX3BUFH  | Extra USART3<br>receive/transmit register<br>(MSB) | E5             | 8-bit word |            |       |        |        | R/W                |        |      |

| SX3FREQL | Extra USART3 frequency<br>divider ratio (LSB)      | E6             | 8-bit word |            |       |        |        | R/W                |        |      |

| SX3FREQH | Extra USART3 frequency divider ratio (MSB)         | E7             | 8-bit word |            |       |        |        | R/W                |        |      |

| SX4CON1  | Extra USART4 configuration 1                       | E9             | MODE1      | MODE0      | ME2   | ME1    | ME0    |                    |        | R/W  |

| SX4CON2  | Extra USART4 configuration 2                       | EA             |            |            | RB8/E | OR/BOT | TI     |                    | RI     | R/W  |

| SX4BUFL  | Extra USART4                                       | EB             |            |            |       | 8-bi   | t word |                    |        | R/W  |

ADV Engineering, Parc technologique du canal, 16 avenue de l'Europe, 31520 Ramonville Saint Agne (France)

# **ADV 80S32**

V 2.5 - 22/05/01

| SYMBOL   | DESCRIPTION                                        | DIRECT<br>ADDR | BIT ADDRESS, SYMBOL, OR ALTERNATIVE PORT FUNCTION |          | ACCESS |

|----------|----------------------------------------------------|----------------|---------------------------------------------------|----------|--------|

|          |                                                    | (Hex)          | MSB                                               | LSB      |        |

|          | receive/transmit register<br>(LSB)                 |                |                                                   |          |        |

| SX4BUFH  | Extra USART4<br>receive/transmit register<br>(MSB) | EC             | 8-b                                               | bit word | R/W    |

| SX4FREQL | Extra USART4 frequency divider ratio (LSB)         | ED             | 8-b                                               | bit word | R/W    |

| SX4FREQH | Extra USART4 frequency<br>divider ratio (MSB)      | EE             | 8-I:                                              | bit word | R/W    |

\* Bit addressable

The 80S32 implements two data pointers. At any time only one of them is selected and can be use as the DPTR register. DPSEL SFR is the data pointer selection register. It works in a similar way to the Philips and Siemens device, e.g. the least significant bit is used to determine which DPTR is selected. The fastest way to swap between data pointer is to use the INC DPSEL instruction. The double DPTR implementation enables faster block data transfers in the external memory, the first register being loaded with the source address and the second one with the destination address. The transfer is then a loop that reads data from the source address, increments DPTR, changes DPTR selection, writes data to the destination address, increments DPTR and changes DPTR selection. DPSEL also acts on the DTBANK register (cf. 3.4.5).

# 3. MEMORY ORGANIZATION

#### 3.1 Introduction

All 8052/51 devices have separate address spaces for program and data memory.

The program memory space is external and can only be read and not written. Up to 64KBytes of the program memory can be accessed by using the PSEN (Program store enable) signal as a read strobe signal.

The data memory space occupies a separate address space from the program memory. The lowest 256 bytes of the data memory space (the internal block) are on chip while up to 64 Kbytes of the external data memory can be accessed for read operation by asserting the Rd\_n signal or write operation by asserting the Wr\_n signal.

The 80S32 device is fully compatible with this organization and adds the possibilities:

- to download a program in RAM and to execute it from this RAM,

- to extend the data memory space up to 16 Mbytes accessible by page of 64 Kbytes,

- to extend the program memory space up to 8 Mbytes arranged in page of 32 Kbytes,

- to share one RAM device between program and data,

- to protect with an EDAC the accesses to the program and data memory spaces,

- to remap addresses 0000<sub>H</sub> to 00FF<sub>H</sub> of the external memory to an on chip 256 bytes RAM block, which is separated from the internal block. This eXtra block can be used in small applications to avoid the use of an external memory.

In addition the 80S32 microcontroller implements a CS generator unit that will avoid the need to add an external decoder in many cases.

#### 3.2 Internal Memory

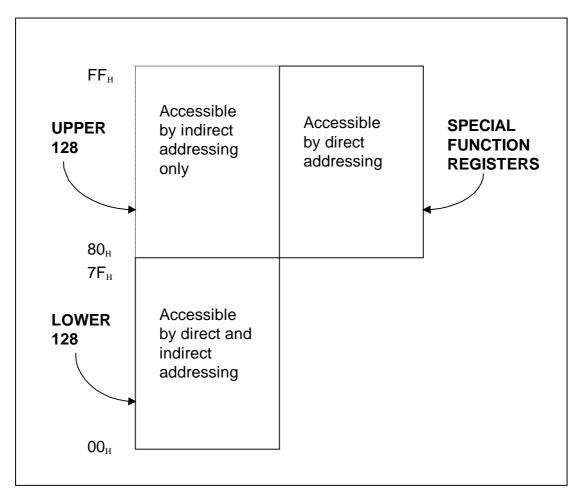

The original 8052/51 has 256 bytes of register RAM and a number of SFRs that are collectively known as internal data memory. The internal data memory is divided into three blocks, which are referred to as the Lower 128, Upper 128 and SFR space. Although the internal data memory address space is only 8-bits wide, it can accommodate more than 256 registers by processing differently direct access and indirect access instructions. Direct access instructions with addresses higher than  $7F_{\rm H}$  always access the SFR space, while indirect accesses with addresses higher than  $7F_{\rm H}$  access the upper 128 space.

All the SFR have been presented in the beginning of the document (cf. § 2). In the rest of the document the term internal memory will apply to the upper 128 and lower 128 address spaces.

**ADV 80S32** V 2.5 - 22/05/01

#### 3.2.1 Lower 128 Bytes: Address 00<sub>H</sub> - 7F<sub>H</sub>

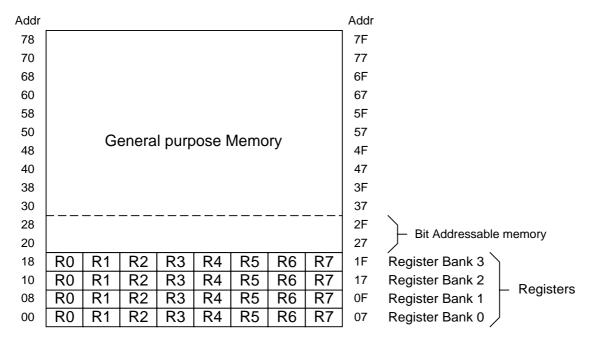

The structure of the lower 128 bytes space is presented in the figure here-above:

The lowest 32 bytes of the space are used for the Register Banks. The ADV 80S32 implements four Register Banks. Only one Register Bank can be used at a time and the selection of Register Bank is controlled by bits RS1 and RS0 in the Processor Status Word SFR (PSW).

Addresses  $20_{\rm H}$  to  $2F_{\rm H}$  implement a general-purpose memory that is bit addressable. The address of a bit is defined by its position in this area. Bit address 0 is located in bit position 0 (least significant position) of the byte address  $20_{\rm H}$ , bit address 1 is located in bit position 1 of the byte address  $20_{\rm H}$ , and so on up to bit  $7F_{\rm H}$  which is located in bit position 7 (most significant bit) of the byte address  $2F_{\rm H}$ . Bit manipulation instruction are presented in §12.5 (more details will be found in RD-1).

Addresses  $30_{\rm H}$  to  $7F_{\rm H}$  is a general-purpose memory that can be accessed either by direct and indirect addressing instructions.

#### 3.2.2 Upper 128 Bytes: Address 80<sub>H</sub> - FF<sub>H</sub>

Addresses  $80_{\rm H}$  to FF<sub>H</sub> form a general purpose memory that can only be accessed by indirect addressing instructions.

#### 3.2.3 Internal Memory protection

The 80S32 has the possibility to protect the internal memory with an EDAC (cf. §3.6).

The EDAC function is enabled by setting the IPCON bit in the MPCON Special Function Register (cf. Figure 3-14). When the internal memory protection is enabled, memory locations  $00_{\rm H}$  to  $7F_{\rm H}$  are used to store data while memory location  $80_{\rm H}$  to  $FF_{\rm H}$  are used to store protection code. Addresses  $80_{\rm H}$  to  $FF_{\rm H}$  are in this case not accessible by software and each access to this part of the memory is re-directed to the requested address modulo  $80_{\rm H}$ . For example, an access to address  $0AB_{\rm H}$  is re-directed to address  $2B_{\rm H}$ .

When enabled, the internal memory protection is transparent to the user. When data is written to an address X, its protection code is calculated by the EDAC and written at address  $X + 80_{H}$ . When data is read from address X, its protection code is read from address  $X + 80_{H}$  and is used to correct the data in real time before being used by the 80S32.

The detection of a recoverable error or a unrecoverable error is flagged in the IMER bits of the MPSTAT register (cf. Figure 3-12) and an interruption is generated if previously enabled (cf. Figure 6-1). The address of the corrupted data is then available in the IXERAD register and has, in the case of a recoverable error, to be used to read and write back the corrupted data in order to refresh it. After error processing the IMER bits shall be reset by software (cf. Figure 3-12).

Enabling the EDAC does not slow down the microprocessor accesses and thus does not degrade the microcontroller performance.

### 3.3 eXtended RAM (XRAM)

The XRAM extends the internal memory space of 256 bytes but is mapped into the external data memory space at addresses  $0000_{\rm H}$  to  $00FF_{\rm H}$  and can therefore only be accessed by using MOVX instructions (cf. RD1). The XRAM can only be used to store data and cannot contain instruction codes.

The use of the XRAM is enabled via the XMAP bit in the SYSCON register (cf. Figure 3-13). When this is done all « MOVX @DPTR,A » and « MOVX A,@DPTR » instructions when 0000H < DPTR < 00FFH and DTBANK = "00", and all « MOVX @Ri,A » and « MOVX A,@Ri » instructions addresses the XRAM instead of the external memory. As a consequence, access to the external memory at address between  $0000_{\rm H}$  and  $00FF_{\rm H}$  in page 0 is not possible when the XRAM is enabled. Considering that XRAM cannot contain instruction code, the XRAM shall always be disabled during downloading of program instructions with an address between  $0000_{\rm H}$  and  $00FF_{\rm H}$ .

The XRAM can also be protected by EDAC similarly to the internal memory. The EDAC is switched on by setting the XPCON bits in the MPCON register (cf. Figure 3-14). When the XRAM protection is enabled, memory location  $00_{\rm H}$  to  $7F_{\rm H}$  are used to store data while memory location  $80_{\rm H}$  to  $FF_{\rm H}$  are used to store protection code.

Addresses  $80_{\rm H}$  to  $FF_{\rm H}$  are not accessible by software and each access to this part of the memory is re-directed to the requested address modulo  $80_{\rm H}$ . For example, an access to address  $AB_{\rm H}$  is redirected to address  $2B_{\rm H}$ .

When enabled, the XRAM protection is transparent to the user. When data is written to an address X, its protection code is calculated by the EDAC and written to address  $X + 80_{H}$ . When data is read from address X, its protection code is read from address  $X + 80_{H}$  and is used to correct the data in real time before being used by the 80S32 core.

The detection of a recoverable error or a unrecoverable error is flagged in the IMER bits of the MPSTAT register (cf. Figure 3-12) and an interruption is generated if previously enabled (cf. §6). The address of the corrupted data is then available in the IXERAD register and has, in the case of a recoverable error, to be used to read and write back the corrupted data in order to refresh it. After error processing the IMER shall be reset by software (cf. Figure 3-12).

Enabling the EDAC does not slow down the microprocessor accesses and thus does not degrade the microcontroller performance.

For programs which do not need much data storage capacity, the use of the XRAM can avoid the use of an external RAM.

## 3.4 External memory

#### 3.4.1 Introduction

As presented in § 3.1, the 80S32 can access two different memory spaces by means of different control signals. PSE\_n is used as the read strobe signal for the program memory space while Rd\_n and Wr\_n are used as the read and write strobe signal of the data memory space (cf. RD 1). In the original 8052/51 PSE\_n is always used for accessing the program memory space while Rd\_n and Wr\_n are always used for accessing the data memory space. We will call this configuration the « ROM program execution».

The 80S32 adds a new possibility that is to use Rd\_n instead of Pse\_n to access program memory. We will call this configuration the « RAM program execution».

After reset, the 80S32 is in the « ROM program execution» mode and can execute a program from an external non-volatile memory (EA = '0') or the internal bootstrap program (EA = '1').

The configuration can then be changed by software at any time via the EMP bit in the EMCON register (cf. Figure 3-11). Each time the configuration is changed, the microcontroller is reset (except the EMCON register) which enables to restart the program execution from address 0 of the RAM when changing from the « ROM program execution» mode to the « RAM program execution» mode or from address 0 of the ROM when changing from the « RAM program execution» mode to the « ROM program execution» mode.

For external memory accesses, the 80S32 uses an 8 bit bi-directional data bus Data(7:0), a 16 bit address bus Add(15:0) and up to 8 bits ExtAd16 to ExtAd23 for extending the address bus up to 24 bits. ExtAd23 has different meaning depending on the fact that the memory protection is enabled or disabled.

When in the « ROM program execution» mode, the differentiation between program and data accesses is performed by the assertion of the PSE\_n or the Rd\_n signal.

In the «RAM Program Execution» all accesses are performed with the Rd\_n signal and the Pse\_n signal is always de-asserted. In this mode, the program and data can be located in the same memory space, generally the same device, or in separated memory spaces. These two subconfigurations are commanded via the EMA bits in the EMCON register (cf. Figure 3-11). In fact, these sub-configurations only impact the on-chip address decoder unit behavior (cf. §3.4.6). When program and data are in separated spaces, for a same address value the differentiation is performed by the CS signal that is asserted. If a CSA signal is asserted then the access addresses the program memory space, while if a CSB signal is asserted then the access addresses the data memory space.

When program and data are in the same memory space then only CSA signals are used both for program and data accesses. In this case the developer can arrange the memory space as he wants provided that:

- the first program instruction shall be located at address 0;

- the first instructions of vectoring programs 0 to 12 shall be located at address x\*8+3 where x represents the number of the interrupt ;

- if more than 8 Mbytes of RAM are implemented then program data shall not be located at an address higher than  $7FFFF_{H}$ .

Provided that all these constraints are respected, the distribution of program and data is user defined.

#### 3.4.2 External memory access

The external memory can be protected by an EDAC. The protection is selectively switched on or off for program and data accesses via the PMCON and DMCON bits in the EMCON register (Figure 3-11).

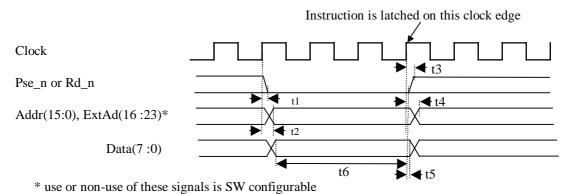

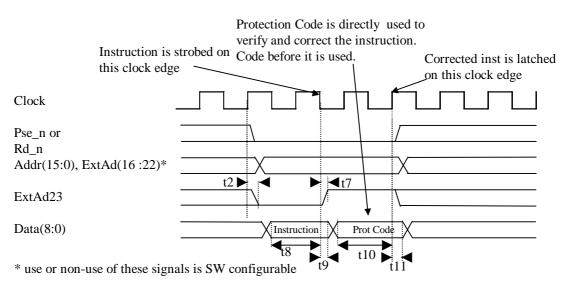

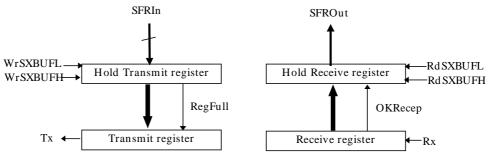

The figures hereafter present how accesses to the program memory are handled in the case where memory protection is disabled (Figure 3-1) and enabled (Figure 3-2). In the two cases, the access is performed in 3 clock cycles minimum but can be longer if the microcontroller is executing an instruction that need more than 3 clock cycles to be processed. When the memory protection is on the ExtAd23 signal is used to indicate if the microcontroller accesses the instruction (ExtAd23 = '0') or the protection code (ExtAd23 = '1'). ExtAd23 is at logic level '0' for 1.5 clock cycle at the beginning of the access and then at logic level '1' for the rest of the access. The data is latched in an intermediate register on the same falling clock edge which sets the ExtAd23 signal to '1' and is corrected in real time with the code present on the bus in the second part of the access before it is used. When the memory protection is off ExtAd23 makes the  $24^{th}$  bit of the address bus.

To speed-up the access, the Pse\_n or the Rd\_n signal is permanently asserted for program accesses as long as no external memory data access is needed.

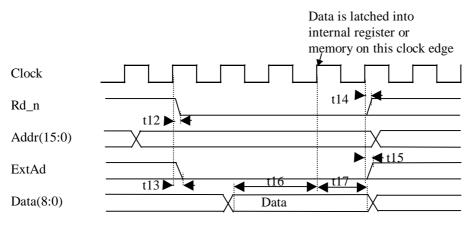

Figure 3-1: Program access with memory protection off

Figure 3-2: Program access with memory protection on

The minimum access time of the memory devices used to store the program shall be equal to  $3T_{\rm Clock}$ – 2 ns when the memory protection is off, and equal to 1,4  $T_{\rm Clock}$ – 8ns when the memory protection is on. However to accommodate slow devices it is possible to insert between 1 and 15 wait states of 1  $T_{\rm Clock}$  in all program accesses, which increase the minimum access time between 1 and 15  $T_{\rm Clock}$  (cf. §3.4.3).

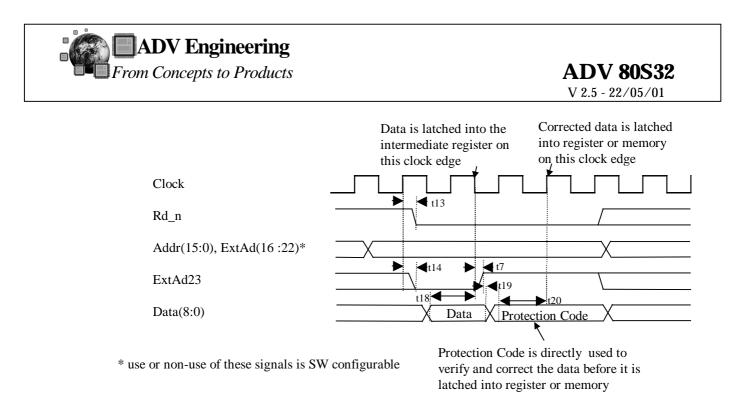

The figures hereafter present how read accesses to the data memory are handled in the case when memory protection is off (Figure 3-3) or on (Figure 3-4).

In both cases, the access is performed in 4 clock cycles. When the memory protection is on then the ExtAd23 signal is used to indicate if the microcontroller accesses the instruction (ExtAd23 = '0') or the protection code (ExtAd23 = '1'). ExtAd23 is at logic level '0' for 1.5 clock cycles at the beginning of the access and then at logic level '1' for the rest of the access. The data is latched in an intermediate register 1.5 clock cycles after the beginning and it is corrected in real time with the data present on the bus in the second part of the access before it is used.

Figure 3-3: Read data access with memory protection off

Figure 3-4: Read data access with memory protection on

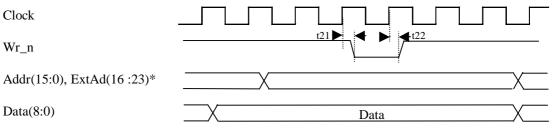

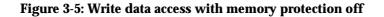

The figures hereafter present how write accesses to the data memory are handled in the case when memory protection is off (Figure 3-5) or on (Figure 3-6).

In both cases, the access is performed in 7 clock cycles. When the memory protection is on then the ExtAd23 signal is used to indicate if the microcontroller outputs data on the data bus (ExtAd23 = '0') or a protection code (ExtAd23 = '1'). The design guarantees that when Wr\_n is asserted then all the signals ExtAd(23-16), Add and Data are stable. In addition, these signals change only half a clock cycle after the Wr\_n rising edge.

\* use or non-use of these signals is SW configurable

\* use or non-use of these signals is SW configurable

#### Figure 3-6: Write data access with memory protection on

The minimum access time of the memory devices used to store the program shall be equal to  $3T_{Clock}$ – 2 ns when the memory protection is off, and equal to 1,4  $T_{Clock}$ – 8 ns when the memory protection is on. In addition the minimum write pulse duration shall be less than 1  $T_{clock}$ . However to accommodate slow devices it is possible to insert between 1 and 15 wait states of 1  $T_{Clock}$  in all program accesses, which increase the minimum access time between 1 and 15  $T_{Clock}$  (cf. §3.4.3).

## 3.4.3 Wait states insertion

The ADV80S32 gives the possibility to include between 1 and 15 Wait States into program and data accesses. Wait state insertions is compatible with both the ROM program execution and the RAM program execution mode, and also with memory protection scheme. The number of Wait States to be inserted is defined into the WaitMem SFR which is presented in the figure hereafter.

| SFR @ | (MSB) | (LSB) |

|-------|-------|-------|

| 0С3н  | WSPA  | WSDA  |

| Symbol | Significance in write mode                                                                                                         | Significance in read mode |

|--------|------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| WSPA   | Wait states for program accesses. This field shall be used to program the number of wait states to insert during program accesses. |                           |

| WSDA   | Wait states for data accesses. This field shall be used to program the number of wait states to insert during program accesses.    |                           |

#### Figure 3-7: WAITMEM register

WAITMEM register acts on the length of the Pse\_n, Rd\_n and Wr\_n pulses by extending their duration of WSPA  $T_{elock}$  for a program memory access and WSDA  $T_{elock}$  for a data memory access. During read operations and when the memory protection is on, the 80S32 reads two data in the same cycle (cf. Figure 3-2 and Figure 3-4) WSPA or WSDA waits states are inserted both for the acquisition of the data and for the acquisition of the protection code (e.g. before and after the ExtAd23 rising edge).

#### 3.4.4 External Memory Protection

The EMCON register allows to activate memory protection for both the program memory accesses and data memory accesses. EDAC for program accesses can be switched on or off with the PMCON bits of the EMCON register, while the EDAC for data accesses can be switched on or off with the DMCON bit in the EMCON register.

When the external memory protection is used, the EXTAD23 output shall be enabled in the EXTBUS register (cf. 3.4.5). It shall be used externally to differentiate between data accesses (EXTAD23 = '0') and protection code accesses (EXTAD23 = '1').

When an error is detected during a program access, it is flagged in the PG\_ER\_FLAG bits in the MPSTAT register and an interrupt is generated if it was previously enabled (cf. Figure 3-12). The location address of the error can be found in the PDERADH (MSB) and PDERADL (LSB) registers. After the error has been processed the PG\_ER\_FLAG has to be reset by SW (by writing in the MPSTAT register, cf. Figure 3-12).

The 80S32 process in the same way errors detected during data accesses, except that an error is in this case flagged in the DT\_ER\_FLAG bits of the MPSTAT register.

### 3.4.5 Memory banks

The ADV80S32 enable to extend the external memory spaces up to 8 Mbytes for program and 16 Mbytes for the code by using page memory schemes.

To support memory banks the address bus can be extended from 16 bits to 24 bits via the EXTBUS register presented in the figure hereafter:

| SFR @         | (MSB)   |         |         |         |         |         |         | (LSB)   |

|---------------|---------|---------|---------|---------|---------|---------|---------|---------|

| $0B5_{\rm H}$ | EXTAD23 | EXTAD22 | EXTAD21 | EXTAD20 | EXTAD19 | EXTAD18 | EXTAD17 | EXTAD16 |

| Symbol  | Significance in write mode                                                                                                                                             | Significance in read mode                                                                                                                         |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| EXTAD16 | <ul> <li>Program memory configuration:</li> <li>'0': configure P0.7 as an IO port</li> <li>'1': configure P0.7 is the 17<sup>th</sup> address bit</li> </ul>           | <ul> <li>Program memory configuration:</li> <li>'0': P0.7 as an IO port</li> <li>'1': P0.7 is the 17<sup>th</sup> address bit</li> </ul>          |

| EXTAD17 | <ul> <li>Program memory configuration:</li> <li>'0': configure P0.6 as an IO port</li> <li>'1': configure P0.6 is the 18<sup>th</sup> address bit</li> </ul>           | <ul> <li>Program memory configuration:</li> <li>'0': P0.6 as an IO port</li> <li>'1': P0.6 is the 18<sup>th</sup> address bit</li> </ul>          |

| EXTAD18 | <ul> <li>Program memory configuration:</li> <li>'0': configure P0.5 as an IO port or CSB_2*</li> <li>'1': configure P0.5 is the 19<sup>th</sup> address bit</li> </ul> | <ul> <li>Program memory configuration:</li> <li>'0': P0.5 as an IO port or CSB_2</li> <li>'1': P0.5 is the 19<sup>th</sup> address bit</li> </ul> |

| EXTAD19 | <ul> <li>Program memory configuration:</li> <li>'0': configure P0.4 as an IO port or CSB_1*</li> <li>'1': configure P0.4 is the 20<sup>th</sup> address bit</li> </ul> | <ul> <li>Program memory configuration:</li> <li>'0': P0.4 as an IO port or CSB_1</li> <li>'1': P0.4 is the 20<sup>th</sup> address bit</li> </ul> |

| EXTAD20 | <ul> <li>Program memory configuration:</li> <li>'0': configure P0.3 as an IO port or CSB_0*</li> <li>'1': configure P0.3 is the 21<sup>st</sup> address bit</li> </ul> | <ul> <li>Program memory configuration:</li> <li>'0': P0.3 as an IO port or CSB_0</li> <li>'1': P0.3 is the 21<sup>st</sup> address bit</li> </ul> |

| EXTAD21 | <ul> <li>Program memory configuration:</li> <li>'0': configure P0.2 as an IO port or CSA_2*</li> <li>'1': configure P0.2 is the 22<sup>nd</sup> address bit</li> </ul> | <ul> <li>Program memory configuration:</li> <li>'0': P0.2 as an IO port or CSA_2</li> <li>'1': P0.2 is the 22<sup>nd</sup> address bit</li> </ul> |

**ADV 80S32**

| EXTAD22 | <ul> <li>Program memory configuration:</li> <li>'0': configure P0.1 as an IO port or CSA_1*</li> <li>'1': configure P0.1 is the 23<sup>rd</sup> address bit</li> </ul>                      | CSA_1                                                                 |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

| EXTAD23 | <ul> <li>Program memory configuration:</li> <li>'0': configure P1.2 as an IO port</li> <li>'1': configure P1.2 is the 24<sup>th</sup> address bit or used for memory protection.</li> </ul> | • '1': P1.2 is the 24 <sup>th</sup> address bit<br>or used for memory |

\* Configuration between port and CS function is selected with the PODIR SFR register

#### Figure 3-8: EXTBUS register

Each bit can be individually configured. For program memory space, paging mechanism takes care that the interrupt vector table located in the program memory between address 0 and  $73_{\rm H}$  shall be accessible at any time and that the instruction flow shall not be disturbed during pages switching. To do so, the program memory between addresses  $0000_{\rm H}$  and  $7\rm{FFF}_{\rm H}$  is used as a common memory that does not support paging and the program memory between addresses  $8000_{\rm H}$  and  $\rm{FFFF}_{\rm H}$  is used as a paged memory where the accessed page can be selected via the CODBANK 8-bit register.

Starting from the 8032 16-bit address, the chip elaborates the 23-bit code address as follow:

- if 0 <= 8032 address <  $8000_{\rm H}$  then the 23-bit address is a concatenation of 7-bit to '0' with the 8032 address,

- if  $8000_{\rm H} \le 8032$  address < FFFF<sub>H</sub> then the 23-bit address is a concatenation of the CODBANK register with the 15 least significant bit of the 8032 address.

Common memory will be used to host the interrupt vector table, the page switching routines and others user defined routines which can be accessed independently from the selected page. The paged memory will be used to host the rest of the program that shall be broken down into blocks of 32 Kbytes and distributed into the available pages.

Many compilers and linkers support bank switching, and many of them include library functions for page switching. The documentation accompanying your compiler will provide information concerning its expanded memory support.

For data memory space the paging is implemented on the whole address range and a 24-bit address is elaborated by concatenating the DTBANK register with the 16-bits of the 8032 address. However, when the external memory protection is on, the most significant bit of DTBANK is not used and ExtAD23 is used as an indicator of the access ('0' = data access, '1' = code access).

As for the DPTR register, the DTBANK register is doubled. At any time one of them is selected and used to elaborate the address for all data memory access. Selection between the two registers is performed with the DPSEL register. This mean that to each DPTR register is associated a DTBANK register that enable faster block data transfers between banks.

Access to the XRAM with MOVX A,@DPTR and MOVX @DPTR,A instructions is only possible when DTBANK = 0. When DTBANK is different from 0, MOVX A,@Ri and MOVX @Ri,A shall be used for all accesses to XRAM.

#### 3.4.6 On-chip address decoder unit

For applications not needing more than 128 Kbytes of protected or unprotected memories, the 80S32 provides an on-chip address decoder unit that can avoid the use of extra glue logic between the microcontroller and the memory. The microcontroller can manage up to 6 chip select signals, 3 for the program memory space and 3 for the data memory space.

The CS generation is performed in two stages. The first stage performs the address decoding and generates 6 CS signals, 3 for program accesses and 3 for data accesses.

The decoding function depends on the size of the memory devices used to implement the program memory space and data memory space (which is defined via the CSCON register cf. Figure 3-10) and whether the memory accesses are protected by EDAC or not (which is defined in the EMCON register cf. Figure 3-11). The table hereafter summarizes the possible configurations and the values of the Add and ExtAd signals for which CS signals are asserted.

| Device<br>size | Memory<br>protection | CS0 and CS3*  | CS1 and CS4*    | CS2 and CS5*    |

|----------------|----------------------|---------------|-----------------|-----------------|

| 8K             | protected            | 0 < Add < 4K  | 4K < Add < 8K   | 8K < Add < 12K  |

| 8K             | unprotected          | 0 < Add < 8K  | 8K < Add < 16K  | 16K < Add < 24K |

| 32K            | protected            | 0 < Add < 16K | 16K < Add < 32K | 32K < Add < 48K |

| 32K            | unprotected          | 0 < Add < 32K | 32K < Add < 64K | 0K < Add < 32K  |

|                |                      | and EXTAD16=0 | and EXTAD16=0   | and EXTAD16=1   |

| 128 K          | protected            | always set    |                 | -               |

| 128 K          | unprotected          | always set    | -               | -               |

$\ast$  CS0, CS1 and CS2 are unset during data memory accesses; CS3, CS4 and CS5 are unset during program memory accesses.

The second stage is used to route the program access CS signals (CS0, CS1, CS2) and data access CS signals (CS3, CS4, CS5) onto the microcontroller interface signals CSA\_0, CSA\_1, CSA\_2 and CSB\_0, CSB\_1, CSB\_2 (all signals are low level active).

The connection between these signals is depending on the External Memory Access type defined in the EMA bits (cf. Figure 3-11) and are presented in the table hereafter:

| Configuration | CSA_0      | CSA_1      | CSA_2      | CSB_0 | CSB_1 | CSB_2 |

|---------------|------------|------------|------------|-------|-------|-------|

| EMA = '01'    | CS3        | CS4        | CS5        | N.U.  | N.U.  | N.U.  |

| EMA = '11'    | CS0        | CS1        | CS2        | CS3   | CS4   | CS5   |

| EMA = '10'    | CS0 or CS3 | CS1 or CS4 | CS2 or CS5 | N.U.  | N.U.  | N.U.  |

Note: EMA = '00' not used

As defined, the address decoder function is compatible with the program-downloading feature. The downloading program can either be the internal bootstrap program or a program stored in an external ROM accessed with the Pse\_n signal. If data and program share the same memory space, the memory devices used to store data and memory shall be connected to the CSA signals. If not the memory devices used to store the program shall be connected to the CSA signals while the memory devices used to store data shall be connected to the CSB signals.

After reset the microcontroller is in the « ROM program execution» mode and executes the onchip downloading routine (EA = '1') or the program stored in an external PROM (EA = '0'). In this configuration, all accesses to the data memory space are addressing devices connected to the CSA signal. After program downloading, the last action of the bootstrap program shall then be to enter the « RAM Program Execution» mode that causes the device to be reset and to start the execution of the program from RAM address 0.

In the « RAM Program Execution» mode all accesses to the data program space are addressing devices connected to the CSA signals that corresponds to the RAM where the program has been downloaded. Concerning data, depending whether the « separated RAM configuration » or « shared RAM configuration » is in use then all accesses will address devices connected to the CSB signals or the CSA signals.

## 3.4.7 Memory organization summary

The table hereafter summarizes the different physical memory spaces that are used by the 80S32 and their use depending on the selected configuration mode.

|                                                                                                                                 | ROM Space | RAM Space                                        | RAM Extension Space             |

|---------------------------------------------------------------------------------------------------------------------------------|-----------|--------------------------------------------------|---------------------------------|

| Memory                                                                                                                          | ROM       | RAM                                              | RAM                             |

| Maximum size                                                                                                                    | 8M*8      | 16M*8                                            | 16M*8                           |

| control signal                                                                                                                  | Pse_n     | Rd_n and Wr_n                                    | Rd_n and Wr_n                   |

| Selection signal                                                                                                                | Pse_n     | CS_A                                             | CS_B                            |

| use of addresses 0 to 7FFFFF <sub>H</sub>                                                                                       |           |                                                  |                                 |

| 'ROM Program Access' mode                                                                                                       | Program   | Data,                                            | unused,                         |

| 'Separated RAM program Access' mode                                                                                             | U         | program                                          | data                            |

| 'Shared RAM program Access' mode                                                                                                |           | Program and data                                 | unused                          |

| use of addresses 800000 <sub>H</sub> to FFFFFF <sub>H</sub><br>'ROM Program Access' mode<br>'Separated RAM program Access' mode | unused    | data or protect. Code<br>Unused or Protect. Code | unused<br>data or protect. Code |

| 'Shared RAM program Access' mode                                                                                                | unused    | data or protect. Code                            | unused                          |

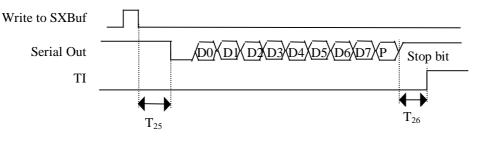

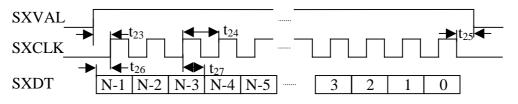

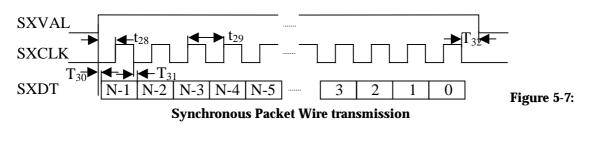

Memory of the 80S32 is split into 3 different physical spaces, the ROM space, the RAM space and the RAM extension space. The ROM space corresponds to the program space of the original 8051 and contains the code to be executed after a reset when EA = 0. It can be the application program or a bootstrap to download the application program into the RAM. Access to the ROM space is always indicated with Pse\_n at logic level '0' and Rd\_n and Wr\_n are never asserted for ROM accesses.