# Atmel®

# **Workshop FPGA ESA November 5**th, 2012

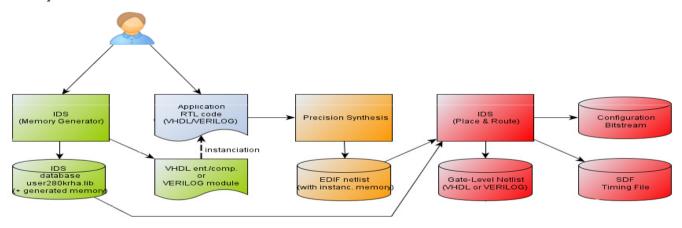

Design flow precision - IDS

#### **AGENDA**

- Precision

- Precision constraints from IDS

- Improved customer design

- Target for timing improvement in IDS

- Application notes

#### **PRECISION**

New production release: Precision Synthesis OEM 2012b

#### Main Behavior by default:

- GCLKBUF and RSBUF automatically inserted

- max fanout: 100

- Replicate as max fanout strategy (setup\_design -max\_fanout\_strategy = none)

- Flatten netlist

- No register in the pads

```

New variable: Setup_design -atmel_map_option { option(s) }

5 Options: lpm, no_lpm, single_output_macros, dual_output_macros and no_flatten_hierarchy

By default t lpm and single_output_macros

```

By default: Ipm and single\_output\_macros

More efficient option: dual\_output\_macros (FGEN2(T), FGEN2R(T), FGEN1R(T), MGEN, and MGENR(T))

Old variables: warning message

## PRECISION (suite)

#### **Optimization:**

- Minimum timing constraint :

create\_clock to define all the clocks in the design

- More efficient atmel\_map\_option : dual\_output\_macros

- Retiming option is now available

- lower max fanout value :

- General max value : setup\_design -max\_fanout=30,

- Max value for a net: set\_attribute -net ce20 -name max\_fanout value 2

- I/O pads with register: only if there are timing constraints at the design interface

- set\_attribute -design RTL -name INFF/OUTFF/TRIFF -value true -port name To inplement IBUFR you have to forbib OBUFR insertion

#### **Precision constraints from IDS**

- 8 GCK and 4 FCK :

- External clocks and now derived clocks can use GCK

- Only 2 from 4 FCK usable (one per column)

- Only one global reset available (RSBUF): The global can be used now by external or derived reset

Set\_attribute -design RTL -name PRESERVE\_SIGNAL -value true -net <name net> or set\_attribute -design rtl -name MAX\_FANOUT -value <needed value> -net {nreset\_out}

- No unconnected Dout pins for the RAM

- IO pad with register :

- Clock Skew between the core and the periphery

- For each pad type, one global clock per die side

- Memories as black boxes is mandatory

# **Optimisations summary**

|                        | Timing optimisation | Place&route Optimisation |

|------------------------|---------------------|--------------------------|

| Dual_output_macros     | X                   | X                        |

| Retiming               | X                   |                          |

| General max fanout     |                     | X                        |

| Local max fanout       | X                   | X                        |

| I/O pads with register | X                   |                          |

| Memory as black box    |                     | X                        |

## **Example of Improved customer design**

- ACDC3: frequency target 20MHz

- TAS information (november 2009)

Actel RTSX72SU: 31 Mhz (used ressources 69%) Atmel ATF280F: 12 Mhz (used ressources 27%)

Last Atmel P&R (IDS 9.1.3a, precision 2012b) Atmel ATF280F: 18 Mhz (+50%), (used ressources 17 %)

After timing improvement in IDS: expected, 25 MHz

# **Target for timing improvement in IDS**

- Customer design:

- Max frequency from IDS (typ): 29 MHz

- Max frequency measured on board: 40 MHz

- Atmel design:

- Max frequency from IDS (typ): 25 MHz

- Max frequency measured on board: 40 MHz

# **Application notes**

- Available under AEDOS

- Memory generation in IDS in AT40K FPGA family (ref: 41020-AERO-10/12)

• Design Flow ATF280F (ref: 41021A-AERO-10/12: Description from synthesis to final checks (simulation, formal proof)

# **THANK YOU!**

© 2012 Atmel Corporation. All rights reserved.

Atmel®, Atmel logo and combinations thereof, Enabling Unlimited Possibilities®, and others are registered trademarks or trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN THE ATMEL TERMS AND CONDITIONS OF SALES LOCATED ON THE ATMEL WEBSITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS AND PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and products descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless pecifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.