# **TSD** contribution to CWICOM

- > TSD has contributed to the ASIC design and developed the Bit-accurate SW model and the CWICOM Validation & Evaluation Platform.

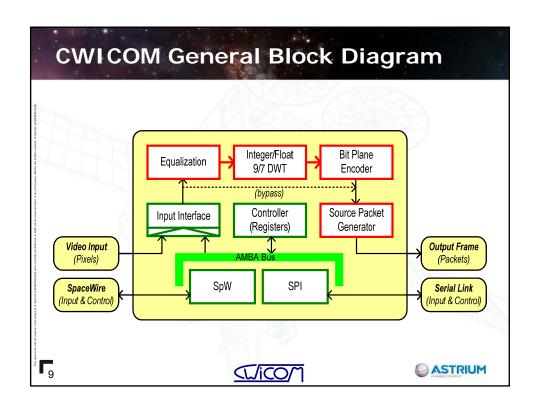

- Contribution to ASIC design:

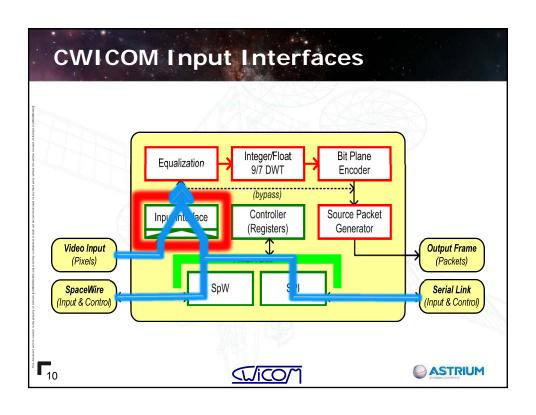

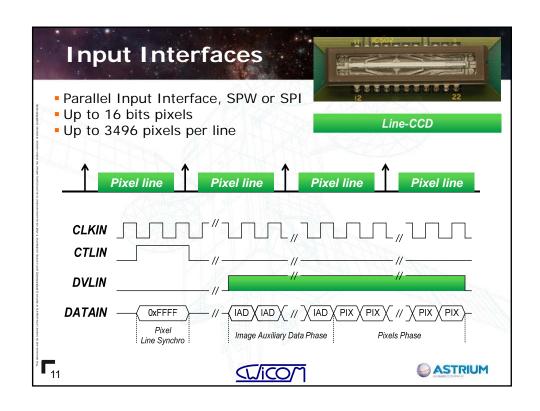

- > Development of the VHDL Input Interface block of CWICOM

- > Integration of the CWICOM VHDL logic

- > System level simulation

# TSD contribution to CWICOM

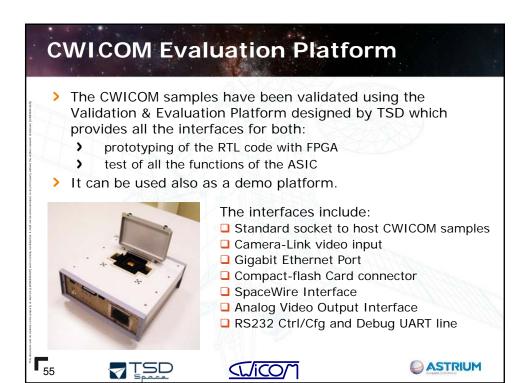

The CWICOM Validation & Evaluation platform provides all the data handling and interface resources to prototype the CWICOM RTL code with FPGA and to test the ASIC samples both in a representative H/W environment.

The CWICOM Validation & Evaluation Platform

I 4

### **CWICOM VHDL Test (TSDev)**

The following activities have been performed:

- Development of the Evaluation and Validation platform based on Xilinx FPGA (design, production and assembly)

- Prototyping of the ASIC design with FPGA by the Evaluation and Validation platform; the CWICOM netlist has been mapped in a Virtex-5LX Fpga by Xilinx.

- Validation of the ASIC design

53

## **Evaluation & Validation Board Usage**

- How the Evaluation & Validation board could support the activities of CWICOM potential users

- The Evaluation and Validation electronic platform developed by TSDev allows a CWICOM potential user:

- the evaluation of ASIC functionalities for test & development purpose

- an easy and economic way for the development of a breadboard which includes a CWICOM equivalent hardware (implemented by Virtex-5 FPGA). The electronic platform could be also customized by TSDev including other interfaces or features.

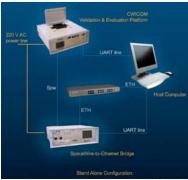

# Verification Test Stand-alone configuration

Stand-alone configuration (Test Mode Configuration) is meant for RTL code prototyping and ASIC validation according to the verification plan

- The full verification database is pre-loaded on CF card.

Test data (image data, configuration files, equalization)

- $\hfill \Box$  Test data (image data, configuration files, equalization parameters...) are read from CF

- ☐ The user send the ID of the Image test to use for validation via UART line using the Serial Commander utility

- ☐ The platform configures CWICOM via SPI interface

- ☐ The selected image is sent via Parallel Input Interface

- ☐ Compressed data are received via Parallel Output Interface

- □ Compressed stream is checked against reference file

- ☐ Test's results are sent via UART line and displayed by Serial Commander utility

The Stand-Alone Configuration

**–**

# **SpaceWire Interface Test**

- ☐ The CWICOM SpaceWire RMAP interface has been tested by using the TSD Ethernet-to-SpaceWire Bridge.

- ☐ The SpaceWire RMAP interface on the Bridge is based on the ESA IP core. This provides an independent tool to validate the CWICOM implementation.

TSD Ethernet-to-Spacewire Bridge

The TSD I/F Bridge is based on a proprietary FPGA based board; it can provide a configurable number and type of communication interfaces (Spacewire, Channel-Link, Camera-Link, GPIO, etc.). The unit implements a bridge between on-

The unit implements a bridge between onboard I/Fs and standard Gigabit Ethernet ports.

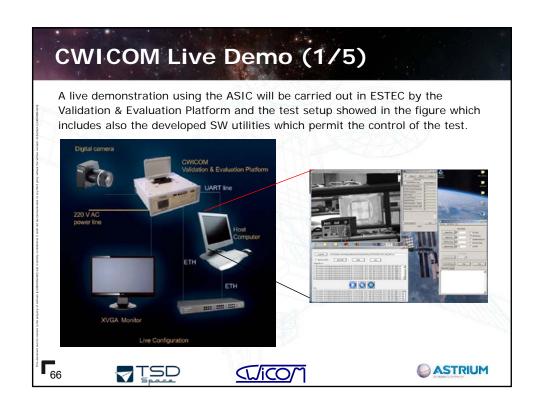

Live configuration is meant to evaluate CWICOM performances in a representative scenario

- Images are received from real camera

- □ Configuration parameters are set via UART line using the Serial Commander utility

- □ CWICOM is configured via SPI interface

- ☐ The images' stream are sent via Parallel Input Interface

- Compressed stream is received via Parallel Output Interface

- □ Compressed stream is sent via UDP to the Host PC

- □ Some utilities on the Host PC will be able to store, decompress and display the compressed video stream

#### **Camera characteristics:**

- CameraLink base configuration, dual-tap

- ☐ Gray-scale Image size of 1600 x 1200

- Pixel dynamics of 10 bit

**-**59

☐ Frame rate up to 60 fps (with binning)

The Live Configuration

### **Verification Test Results**

- For both stand alone and live configurations, all the test procedures specified in the verification plan have been successfully run

- Moreover, further measures and investigations have been carried out in order to acquire significant electrical and timing data relative to the ASIC itself and to estimate the upper limits of the achievable performances

60

**ASTRIUM**

# Further tests & measures Max SysCLK frequency

A subset of the test procedures have been used for an estimation of the limit frequency of the CWICOM itself. For this purpose, the CWICOM SysCLK frequency has been raised progressively up to the condition for which the ASIC output data packets start to contain errors.

The result has been a limit frequency of **72MHz** (for which all procedures run successfully); above 80MHz, all the procedures run with errors.

The last observation suggest that the errors have been due to sampling limits of the Evaluation platform instead of the CWICOM compression itself. This hypothesis has been confirmed by further investigations.

**6**1

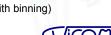

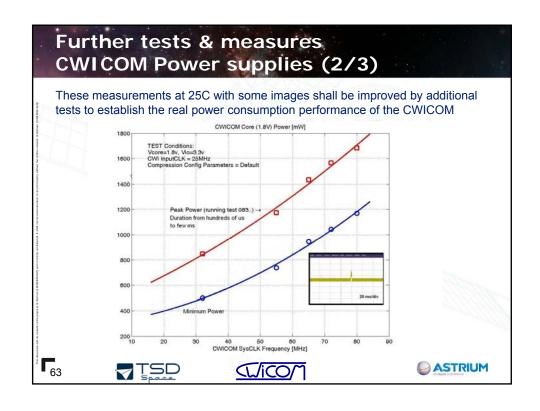

# Further tests & measures CWICOM Power supplies (1/3)

A subset of the test procedures have been carried out with the purpose to estimate the current absorption relating to the 1.8V Core and 3.3V I/O supplies. The results below show that the Core supply absorption is dominant.

| Sys_Clk | Test<br>Procedure | ON<br>current | Peak current |

|---------|-------------------|---------------|--------------|

| 32MHz   | 083               | 278 mA        | 471 mA       |

| 55MHz   | 083               |               | 652 mA       |

|         | 038               | 1             | 559 mA       |

|         | 091               | 410 mA        | 674 mA       |

|         | 092               |               | 678 mA       |

|         | 046               | 4/20          | 594 mA       |

|         | 083               |               | 796 mA       |

| 65MHz   | 038               |               | 708 mA       |

|         | 091               | 525 mA        | 845 mA       |

|         | 092               |               | 818 mA       |

|         | 046               |               | 739 mA       |

|         | 083               |               | 870 mA       |

|         | 038               | 580 mA        | 781 mA       |

| 72MHz   | 091               |               | 927 mA       |

|         | 092               |               | 914 mA       |

|         | 046               |               | 803 mA       |

| 80 MHz  | 091               | 650 mA        | 1007 mA      |

|         | 000               |               | 02E mA       |

| Sys_CLK | Test<br>Procedure | ON current | Peak current |

|---------|-------------------|------------|--------------|

| 55MHz   | 083               | 35 mA      | 110 mA       |

|         | 038               |            | 115 mA       |

|         | 091               |            | 115 mA       |

|         | 092               |            | 75 mA        |

|         | 046               |            | 115 mA       |

| 65MHz   | 083               |            | 128 mA       |

|         | 038               |            | 124 mA       |

|         | 091               |            | 124 mA       |

|         | 092               |            | 75 mA        |

|         | 046               | 128 mA     |              |

| 72MHz   | 083               | TIH        | 128 mA       |

|         | 038               |            | 133 mA       |

|         | 091               |            | 137 mA       |

|         | 092               |            | 75 mA        |

|         | 046               |            | 133 mA       |

Measures on CWICOM 3.3V I/O

Measures on CWICOM 1.8V Core

## CWICOM Live Demo (2/5)

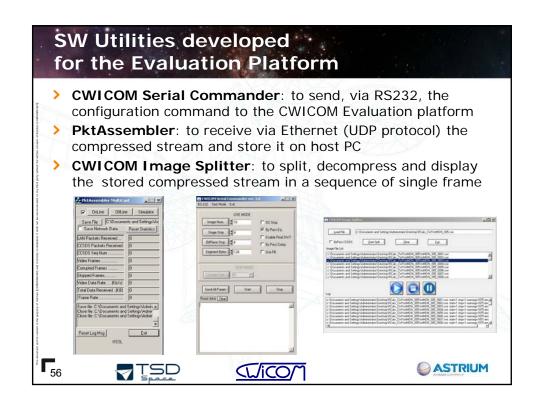

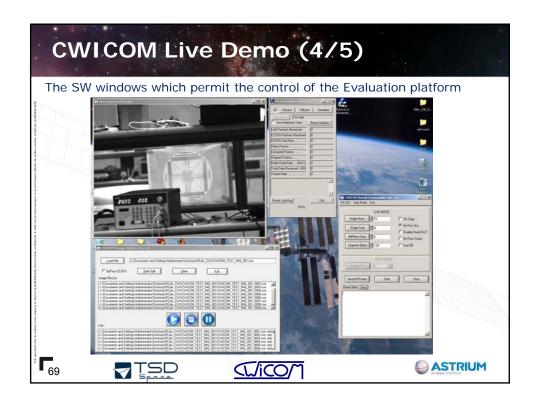

- In the live test configuration the FPGAs of the validation platform are programmed to grab images coming from the camera and to move these to CWICOM via the Parallel Input Interface.

- After power up, using the Serial Commander software, the user must specify the test configuration (that is, type of transform to use, if equalization is to be applied, the number of byte per segment etc.). All these parameters are sent via RS232 serial line to the Evaluation Platform which configures CWICOM via the SPI interface.

- > The compressed data are sent back to the Host Computer via the Ethernet connection using the UDP protocol. Using the Packet Assembler software, it is possible to collect all the UDP packet and save it on the host PC.

- > The saved file then is given in input to the Image Splitter software that reconstructs, decompresses and displays all the images included in the file.

**6**7

### CWICOM Live Demo (3/5)

A typical test sequence consists of the actions listed below:

- ☐ Power-on of the CWICOM Evaluation & Validation Platform

- □ launch and configure the Packet\_Assembler software (set the name and directory of the output file .CWI and other options); "arming" of the SW for waiting for incoming compressed video frames; the software must be placed in the "On Line" state pushing the "On line" button

- □ launch the Serial Commander SW, configure the parameters to send to CWICOM and start the execution of the operations

- wait for completion of the compression (the Packet\_Assembler receives the compressed frames via Ethernet); at the end of the process (the state can be seen by the output of CWICOM on the UART interface) the Packet\_Assembler must be stopped pushing the Off-Line button

- launch the Image\_Splitter and select the .CWI file saved by the Packet\_Assembler, then start the split process

- double click on a single image in the image file list to decompress and visualize the related image

- ush the "Play" button, to start the decompression and visualization process.

## Conclusion

#### **Status**

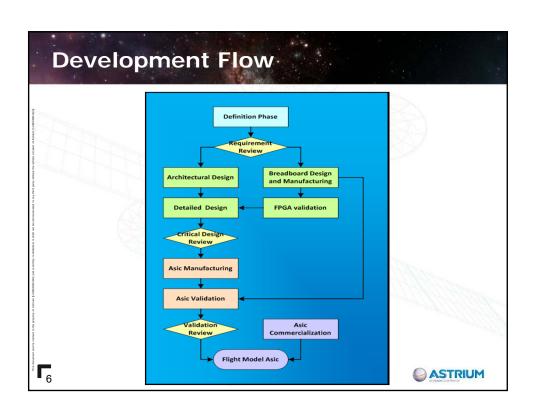

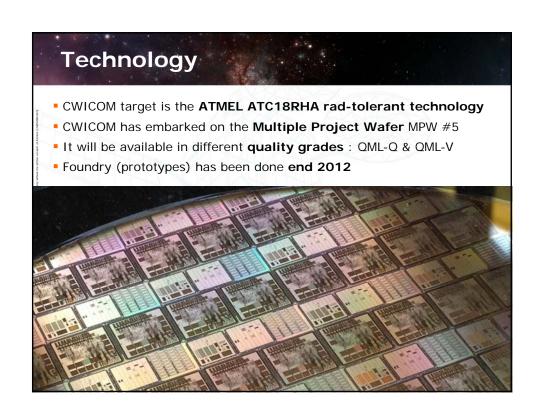

- First foundry has been launched: ASIC prototypes have been successfully validated on a dedicated Compressor Board

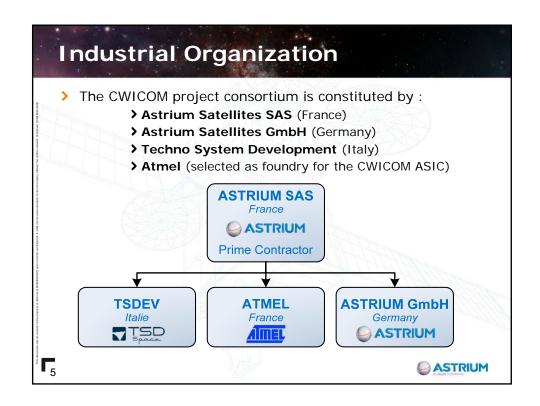

- > CWICOM results from a **fruitful ESA**, **Astrium & TSDEV** collaboration

#### **Next step**

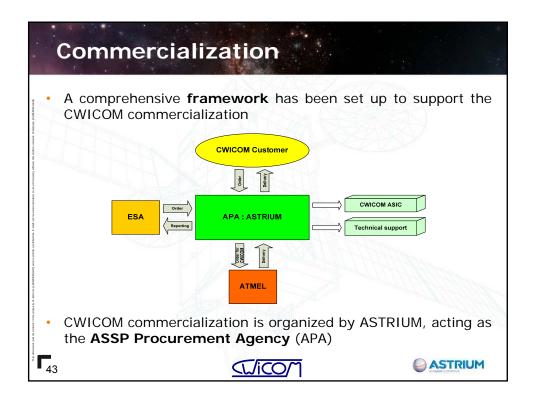

Consolidation with ESA of Commercialization Plan framework (MOQ, price, support...) in order to propose the CWICOM as an ASSP

**1**73

### Conclusion

#### **Summary**

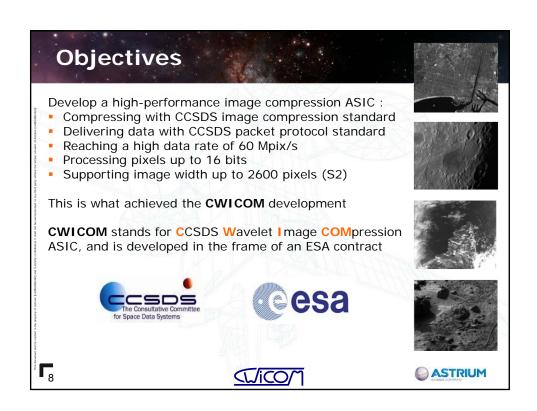

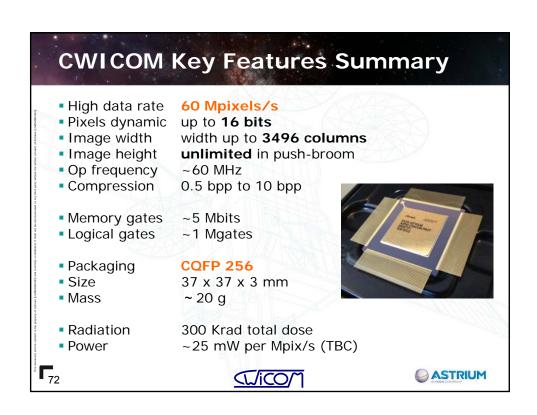

- > The CWICOM ASIC is a high performance image compression ASIC

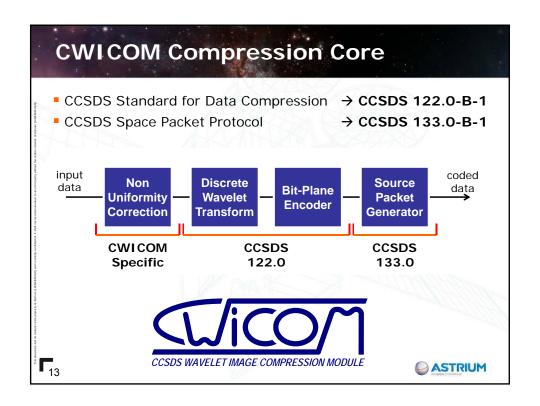

- > Fully compliant with the CCSDS image compression standard

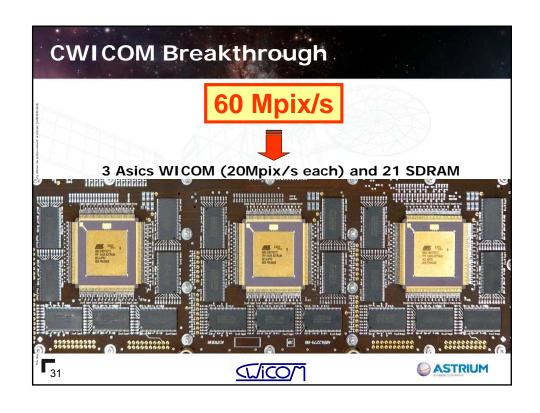

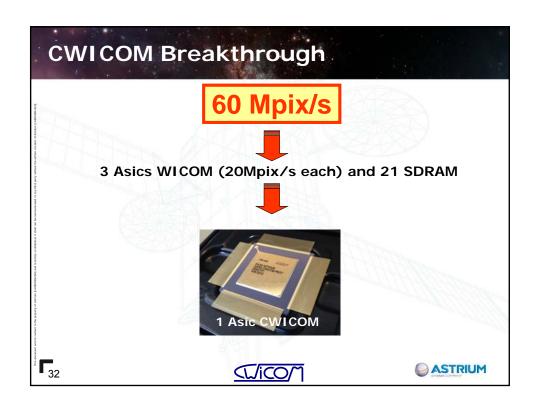

- High data rate performance of 60 Mpix/s

- > Radiation hardened

- Low power consumption

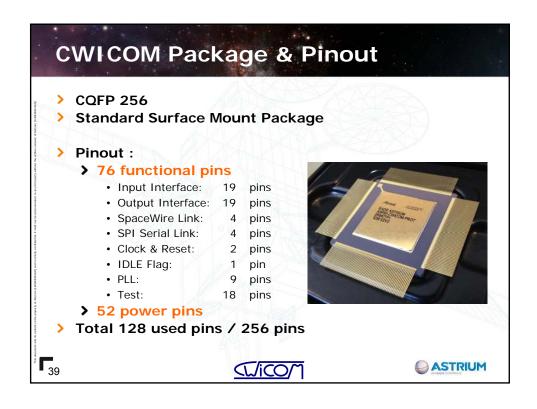

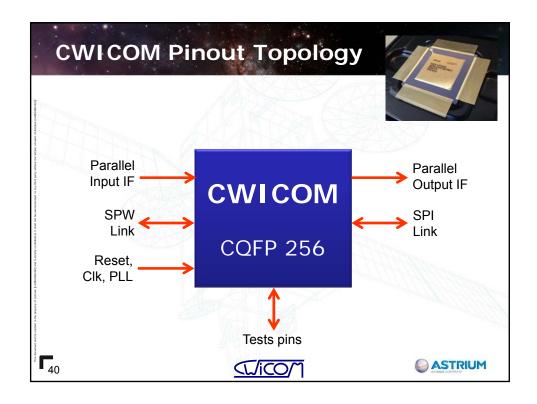

- > Provided in a CQFP256 package easy to mount for SME

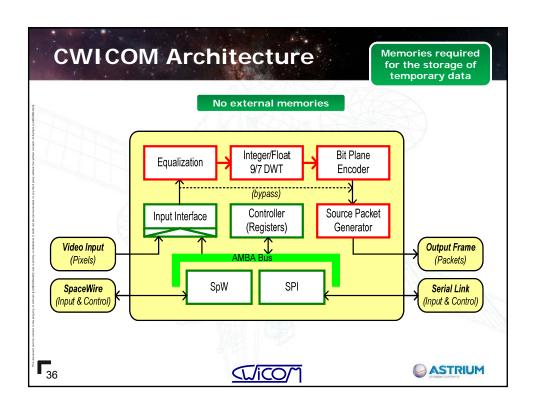

- > No need for any additional external memory

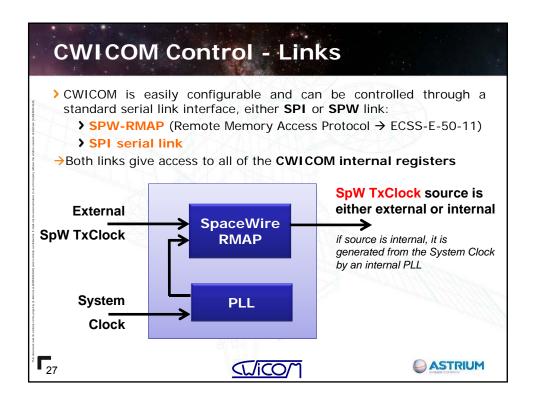

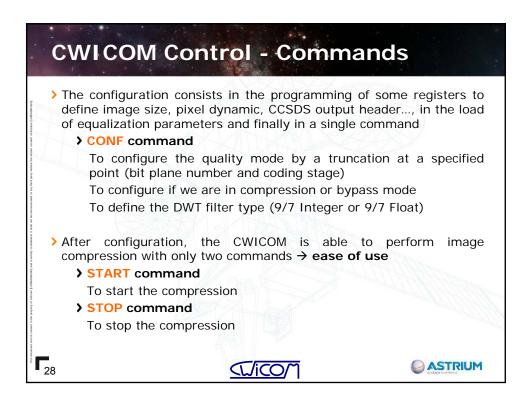

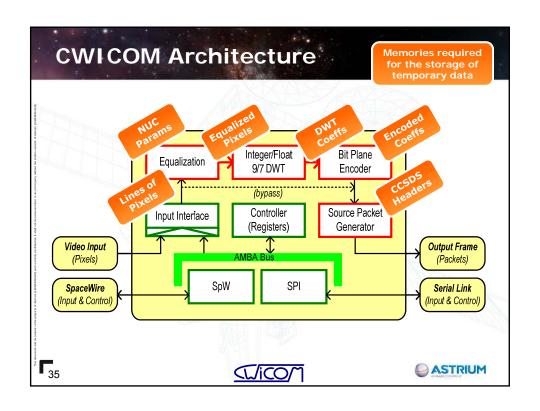

- > Easy to use, with possibility of control through SpW or SPI link

- The CWICOM ASIC has been developed to fulfill the needs of space applications more and more demanding in terms of image compression performances and integration constraints