Ref: R&D.SCOC3.SP.00626.V.ASTR

Issue : 00 Rev.:05 Date : 2007/10/02

Page : i

# ESA R&D n° 20167/06/NL/FM Further Development of the Spacecraft Controller on a Chip

# Specification and Architecture of the SPW-RMAP module

|               | Name and Function                          | Date       | Signature |

|---------------|--------------------------------------------|------------|-----------|

| Prepared by   | <b>Tam LE NGOC</b> Digital Design Engineer | 22/02/08   | Mon       |

| Verified by   | Marc SOUYRI ASIC & FPGA expert             | 22/02/2008 | Cun       |

| Authorized by | Franck KOEBEL SCOC3's project manager      | 22/02/08   | F. Wall   |

| Document type | Nb WBS | Keywords |

|---------------|--------|----------|

|               |        |          |

Ref: R&D.SCOC3.SP.00626.V.ASTR

Issue : 00 Rev. :05 Date : 2007/10/02

Page : ii

### **DOCUMENT CHANGE LOG**

| 2007/04/18   20,21   4590 and 4705 : TX_DESC_ADD and RX_DESC_ADD shall not be modified during a transfer.   27   4830: only current memory area is invalidated.   2830: only current memory and 4040 modified. RST description modified in CTRLREG description. Reset management figure updated.   21,37,38, and 4040 modified. RST description. Reset management figure updated.   21,37,38, and 4040 modified. RST descriptions.   21,37,38, and 4040 modified. RST descriptions described in memory aligned.   21,37,38, and 4040 modified and fire descriptions.   21,37,38, and 4040 modified and 4050: Modification of 17PREG, iTMREG and iTCREG descriptions.   21,37,38, and 4040 modified and 4040: Modification of 17PREG, iTMREG and iTCREG descriptions.   21,37,38, and 4040 modified and 4040: Modification of 4705. Modification of 17PREG, iTMREG and iTCREG descriptions.   24,040: 4240, 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4240; 4 | Issue/<br>Revision | Date       | Modification<br>Nb | Modified pages | Observations                                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------------|--------------------|----------------|-------------------------------------------------------|

| 20,21   shall not be modified during a transfer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 00                 | 2007/04/18 |                    |                |                                                       |

| 33   Details on R/W, R, W and Reserved fields behaviour added.   Introduction of the fact the SW reset shall also last at least 3 CLK_TX cycles.   7,35,64,   4030 and 4040 modified. RST description modified in CTRLREG description. Reset management figure updated.   Paragraph 8.3.1 added, with a new figure describing Reset module.     21,37,38,   ROLLOVER IT added, Modification of 4705. Modification of ITPFREG, ITMREG and ITCREG descriptions.     65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                    |            |                    | 20,21          |                                                       |

| 14   2007/04/30   14   2007/04/30   14   2007/04/30   14   2007/04/30   14   2007/04/30   14   2007/04/30   14   2007/04/30   14   2007/04/30   14   2007/04/30   2007/05/23   2007/05/23   2007/05/23   2007/05/23   2007/10/02   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06   2007/11/06 |                    |            |                    | 27             | 4830: only current memory area is invalidated.        |

| least 3 CLK_TX cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                    |            |                    | 33             |                                                       |

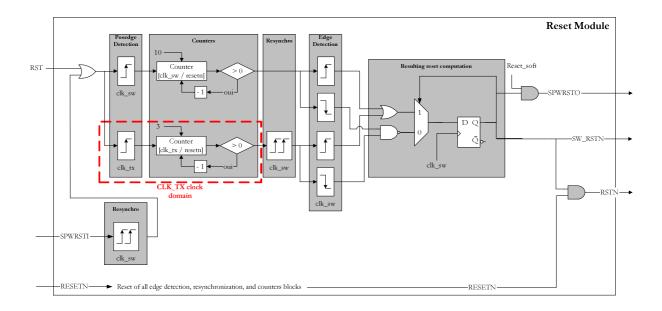

| CTRLREG description. Reset management figure updated.   Paragraph 8.3.1 added, with a new figure describing Reset module.     Paragraph 8.3.1 added, with a new figure describing Reset module.       Paragraph 8.3.1 added, with a new figure describing Reset module.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                    |            |                    |                |                                                       |

| Reset module.   21,37,38,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 01                 | 2007/04/30 | 14                 |                | CTRLREG description. Reset management figure          |

| 39    of ITPFREG, ITMREG and ITCREG descriptions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                    |            |                    |                |                                                       |

| RMW characteristics modifications.   Byte, half-word and word RMW are accepted if memory aligned.   20   4580 : Read replies status is always OK   The specifications modified are: 4240, 4245, 4410, 4730, 4780, 4830, 4840 and 4945.   Adding specifications 4841 and 4856.   The CUR_BUF_END description in table 33 is more accurate.   Modification of the registers.   Adding 4222 and 4223.   Specification modified according to the new interface: 4240, 4245, 4580, 4710, 4730, 4765, 4770, 4775, 4780, 4820, 4830, 4835, 4865, 4890, 4895, 4900, 4905.   The specification 4840 is deleted and the 4901 is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                    |            |                    |                |                                                       |

| 16   Byte, half-word and word RMW are accepted if memory aligned.     02   2007/05/23   1   20   4580 : Read replies status is always OK     16   The specifications modified are: 4240, 4245, 4410, 4730, 4780, 4830, 4840 and 4945.     17   Adding specifications 4841 and 4856.     18   The CUR_BUF_END description in table 33 is more accurate.     18   Modification of the registers.     19   Adding 4222 and 4223.     10   All   Specification modified according to the new interface: 4240, 4245, 4580, 4710, 4730, 4765, 4770, 4775, 4780, 4820, 4830, 4835, 4865, 4890, 4895, 4900, 4905.     19   The specification 4840 is deleted and the 4901 is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                    |            |                    | 65             | Host interface architecture figure updated.           |

| Description of the registers   Description of the registers  |                    |            |                    |                | RMW characteristics modifications.                    |

| The specifications modified are: 4240, 4245, 4410, 4730, 4780, 4830, 4840 and 4945.  All Adding specifications 4841 and 4856.  The CUR_BUF_END description in table 33 is more accurate.  All Modification of the registers.  Adding 4222 and 4223.  Specification modified according to the new interface: 4240, 4245, 4580, 4710, 4730, 4765, 4770, 4775, 4780, 4820, 4830, 4835, 4865, 4890, 4895, 4900, 4905.  The specification 4840 is deleted and the 4901 is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                    |            |                    | 16             |                                                       |

| 4730, 4780, 4830, 4840 and 4945.  All Adding specifications 4841 and 4856.  The CUR_BUF_END description in table 33 is more accurate.  All Modification of the registers.  Adding 4222 and 4223.  Specification modified according to the new interface: 4240, 4245, 4580, 4710, 4730, 4765, 4770, 4775, 4780, 4820, 4830, 4835, 4865, 4890, 4895, 4900, 4905.  The specification 4840 is deleted and the 4901 is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 02                 | 2007/05/23 | 1                  | 20             | 4580 : Read replies status is always OK               |

| The CUR_BUF_END description in table 33 is more accurate.  O4 2007/10/02 All Modification of the registers.  Adding 4222 and 4223.  Specification modified according to the new interface: 4240, 4245, 4580, 4710, 4730, 4765, 4770, 4775, 4780, 4820, 4830, 4835, 4865, 4890, 4895, 4900, 4905.  The specification 4840 is deleted and the 4901 is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                    |            |                    |                |                                                       |

| accurate.  All  All  Modification of the registers.  Adding 4222 and 4223.  Specification modified according to the new interface: 4240, 4245, 4580, 4710, 4730, 4765, 4770, 4775, 4780, 4820, 4830, 4835, 4865, 4890, 4895, 4900, 4905.  The specification 4840 is deleted and the 4901 is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 03                 | 2007/05/23 |                    | All            | Adding specifications 4841 and 4856.                  |

| 04 2007/10/02 All Adding 4222 and 4223.  Specification modified according to the new interface: 4240, 4245, 4580, 4710, 4730, 4765, 4770, 4775, 4780, 4820, 4830, 4835, 4865, 4890, 4895, 4900, 4905.  The specification 4840 is deleted and the 4901 is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                    |            |                    |                |                                                       |

| Adding 4222 and 4223.  Specification modified according to the new interface: 4240, 4245, 4580, 4710, 4730, 4765, 4770, 4775, 4780, 4820, 4830, 4835, 4865, 4890, 4895, 4900, 4905. The specification 4840 is deleted and the 4901 is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 04                 | 2007/10/02 |                    | ΔΙΙ            | Modification of the registers.                        |

| 05 2007/11/06 All 4240, 4245, 4580, 4710, 4730, 4765, 4770, 4775, 4780, 4820, 4830, 4835, 4865, 4890, 4895, 4900, 4905. The specification 4840 is deleted and the 4901 is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 04                 | 2007/10/02 |                    | All            | Adding 4222 and 4223.                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 05                 | 2007/11/06 |                    | All            | 4240, 4245, 4580, 4710, 4730, 4765, 4770, 4775, 4780, |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                    |            |                    |                |                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                    |            |                    |                |                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                    |            |                    |                |                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                    |            |                    |                |                                                       |

NbCars 69942 NbWords 13939 FileName Spec\_Archi\_RMAP\_rev05.doc

© EADS/Astrium

Ref: R&D.SCOC3.SP.00626.V.ASTR

Issue: 00 Rev. :05 Date : 2007/10/02

Page: iii

### PAGE ISSUE RECORD

Issue of this document comprises the following pages at the issue shown

| Page | Issue/<br>Rev. |

|------|----------------|------|----------------|------|----------------|------|----------------|------|----------------|------|----------------|

| 1-76 | 00/00          |      |                |      |                |      |                |      |                |      |                |

| All  | 00/01          |      |                |      |                |      |                |      |                |      |                |

| All  | 00/02          |      |                |      |                |      |                |      |                |      |                |

| All  | 00/03          |      |                |      |                |      |                |      |                |      |                |

| All  | 00/04          |      |                |      |                |      |                |      |                |      |                |

| All  | 00/05          |      |                |      |                |      |                |      |                |      |                |

|      |                |      |                |      |                |      |                |      |                |      |                |

|      |                |      |                |      |                |      |                |      |                |      |                |

|      |                |      |                |      |                |      |                |      |                |      |                |

|      |                |      |                |      |                |      |                |      |                |      |                |

|      |                |      |                |      |                |      |                |      |                |      |                |

|      |                |      |                |      |                |      |                |      |                |      |                |

|      |                |      |                |      |                |      |                |      |                |      |                |

|      |                |      |                |      |                |      |                |      |                |      |                |

|      |                |      |                |      |                |      |                |      |                |      |                |

|      |                |      |                |      |                |      |                |      |                |      |                |

|      |                |      |                |      |                |      |                |      |                |      |                |

|      |                |      |                |      |                |      |                |      |                |      |                |

|      |                |      |                |      |                |      |                |      |                |      |                |

|      |                |      |                |      |                |      |                |      |                |      |                |

|      |                |      |                |      |                |      |                |      |                |      |                |

|      |                |      |                |      |                |      |                |      |                |      |                |

Ref : R&D.SCOC3.SP.00626.V.ASTR

Issue: 00 Rev.:05 Date : 2007/10/02

Page: iv

### **TABLE OF CONTENTS**

| TABLE OF CONTENTSIV                                      |    |  |  |  |

|----------------------------------------------------------|----|--|--|--|

| 1 INTRODUCTION                                           | 1  |  |  |  |

| 2 DOCUMENTS AND ACRONYMS                                 | 3  |  |  |  |

| 2.1 APPLICABLE DOCUMENTS                                 | 3  |  |  |  |

| 2.2 REFERENCE DOCUMENTS                                  | 3  |  |  |  |

| 2.3 ACRONYMS                                             | 4  |  |  |  |

| 3 GENERAL DESCRIPTION OF THE MODULE                      | 5  |  |  |  |

| 4 DETAILED DESCRIPTION OF THE MODULE FUNCTIONALITY       | 7  |  |  |  |

| 4.1 OPERATING MODES                                      | 7  |  |  |  |

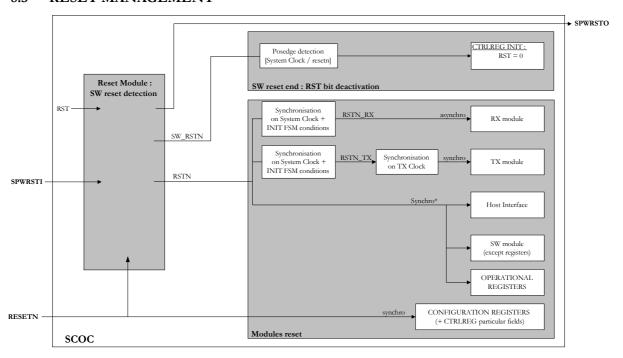

| 4.2 RESET MANAGEMENT                                     | 7  |  |  |  |

| 4.3 SPACEWIRE CORE SPECIFICATION                         | 8  |  |  |  |

| 4.3.1 Link initialization                                | 8  |  |  |  |

| 4.3.2 Transmission function                              | 8  |  |  |  |

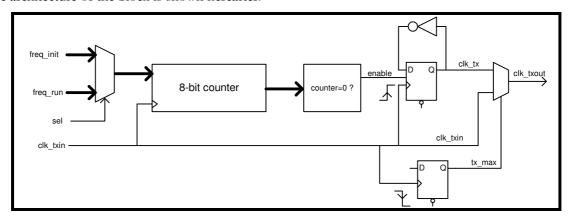

| 4.3.2.1 TX clock programming                             | 9  |  |  |  |

| 4.3.3 Reception function                                 | 9  |  |  |  |

| 4.3.4 Format of the words stored in the TX and RX FIFOs: |    |  |  |  |

| 4.3.5 Link Timing specification                          | 11 |  |  |  |

| 4.4 HOST INTERFACE SPECIFICATION                         | 12 |  |  |  |

| 4.4.1 Functional modes                                   | 12 |  |  |  |

| 4.4.2 Packets structure                                  | 12 |  |  |  |

| 4.4.3 RMAP characteristics                               |    |  |  |  |

| 4.4.3.1 General specification points                     | 15 |  |  |  |

| 4.4.3.2 Write command conformance                        | 16 |  |  |  |

| 4.4.3.3 Read command conformance                         | 17 |  |  |  |

| 4.4.3.4 Read-modify-Write command conformance            |    |  |  |  |

| 4.4.4 AHB interface                                      |    |  |  |  |

| 4.4.5 APB interface                                      |    |  |  |  |

| 4.4.6 TX host interface [THI]                            | 20 |  |  |  |

| 4.4.6.1 Segment descriptors                              | 20 |  |  |  |

| 4.4.6.2 CRC computation                                  | 21 |  |  |  |

| 4.4.6.3 RMAP replies management                          | 22 |  |  |  |

| 4.4.6.4 Transfer management                              |    |  |  |  |

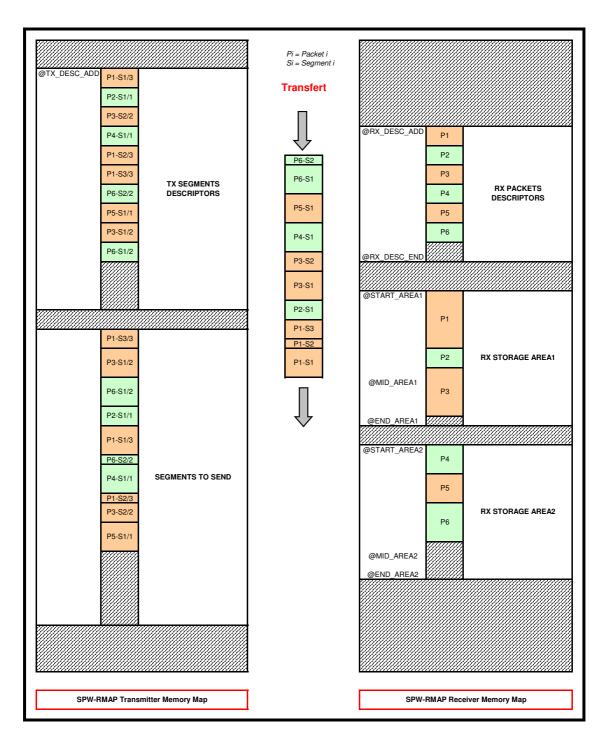

| 4.4.7 RX host interface [RHI]                            |    |  |  |  |

| 4.4.7.1 RX packet descriptors                            |    |  |  |  |

| 4.4.7.2 DATA MODE                                        | 27 |  |  |  |

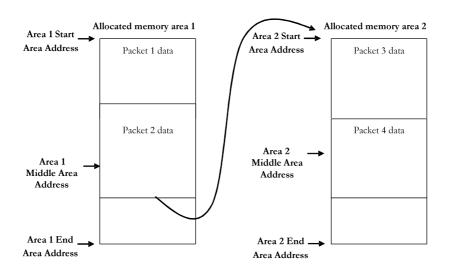

| 4.4.7.2.1 Flip/flop storage mechanism                    | 27 |  |  |  |

Ref : R&D.SCOC3.SP.00626.V.ASTR

Issue: 00 Rev.:05

Date : 2007/10/02

Page : v

|     | 4.4.7.2.2     | Reaching end of packet             | 30        |

|-----|---------------|------------------------------------|-----------|

|     | 4.4.7.2.3     | Reaching the Middle_Area Address   | 30        |

|     | 4.4.7.2.4     | Reaching the End_Area Address      | 30        |

|     | 4.4.7.2.5     | AHB error occurrence               | 31        |

|     | 4.4.7.2.6     | Packet exceeding RX_PKT_SIZE       | 31        |

|     | 4.4.7.2.7     | Hardware flip/flop management      | 31        |

|     | 4.4.7.3       | RMAP MODE                          | 31        |

|     | 4.4.7.3.1     | Reception of a RMAP command        | 32        |

|     | 4.4.7.3.2     | Reception of a RMAP reply          | 34        |

|     | 4.4.7.4       | MIXED MODE                         | 34        |

| 4.5 | Interru       | PTS                                | 35        |

| 4.6 | TIME CO       | DE TRANSMISSION AND RECEPTION      | 35        |

| 4.7 | TEST MO       | DE                                 | 36        |

| 5   | REGISTE       | RS                                 | 37        |

| 5.1 | REGISTE       | RS LIST                            | 37        |

| 5.2 | REGISTE       | RS DETAILED DESCRIPTION            | 38        |

| 6   | MEMORY        | MAPPINGS                           | 45        |

| 7   | INTEREA       | CES                                | 46        |

|     |               |                                    |           |

| 7.1 |               | TERFACE                            |           |

| 7.2 |               | VE INTERFACE                       |           |

| 7.3 |               | STER INTERFACE                     |           |

| 7.4 |               | TERFACE                            |           |

| 7.5 |               | TERFACE                            |           |

| 7.6 |               | PT INTERFACE                       |           |

| 7.7 | Hardwa        | ARE FLIP/FLOP MANAGEMENT INTERFACE | 47        |

| 8   | DETAILE       | D ARCHITECTURE                     | 48        |

| 8.1 | Modific       | CATIONS OVERVIEW                   | 48        |

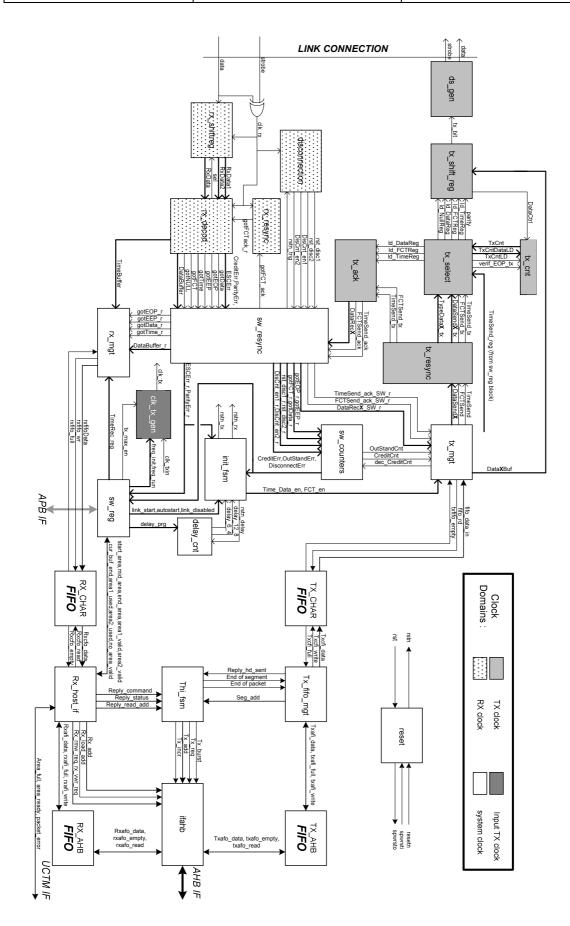

| 8.2 | SPACEWI       | RE CORE ARCHITECTURE               | 49        |

| 8.3 | RESET M       | ANAGEMENT                          | 51        |

| 8   | 2.3.1 Reset N | Module                             | <i>53</i> |

| 8   | 3.3.2 Blocks  | working at TX clock                | <i>53</i> |

|     | 8.3.2.1       | CLK_TX_GEN block                   | 53        |

|     | 8.3.2.2       | DS_GEN block                       | 54        |

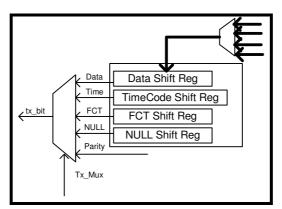

|     | 8.3.2.3       | I'X_SHIFT_REG block                | 54        |

|     | 8.3.2.4       | I'X_SELECT block                   | 54        |

|     | 8.3.2.5       | TX_CNT block                       | 55        |

|     | 8.3.2.6       | TX_ACK block                       | 55        |

|     | 8.3.2.7       | I'X_RESYNC block                   | 55        |

| 8   | 3.3.3 Blocks  | working at RX clock                | 55        |

Ref : R&D.SCOC3.SP.00626.V.ASTR

Issue: 00 Rev.:05

Date : 2007/10/02

Page : vi

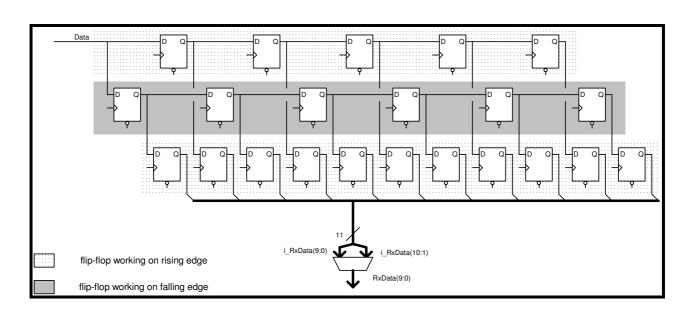

| 8    | .3.3.1  | RX_SHIFTREG block                                       | 56 |

|------|---------|---------------------------------------------------------|----|

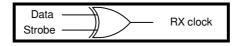

| 8    | .3.3.2  | RX_DECOD block                                          | 57 |

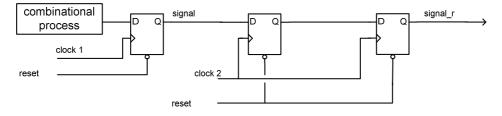

| 8    | .3.3.3  | RX_RESYNC block                                         | 57 |

| 8    | .3.3.4  | DISCONNECTION block                                     | 57 |

| 8.3. | 4 Block | s working at system clock                               | 58 |

| 8    | .3.4.1  | INIT_FSM block                                          | 58 |

| 8    | .3.4.2  | DELAY_CNT block                                         | 58 |

| 8    | .3.4.3  | RX_MGT block                                            | 58 |

| 8    | .3.4.4  | RX_FIFO block                                           | 59 |

| 8    | .3.4.5  | TX_FIFO block                                           | 59 |

| 8    | .3.4.6  | TX_MGT block                                            | 59 |

| 8    | .3.4.7  | SW_COUNTERS block                                       | 60 |

| 8    | .3.4.8  | SW_RESYNC block                                         | 60 |

| 8    | .3.4.9  | SW_REG block                                            | 61 |

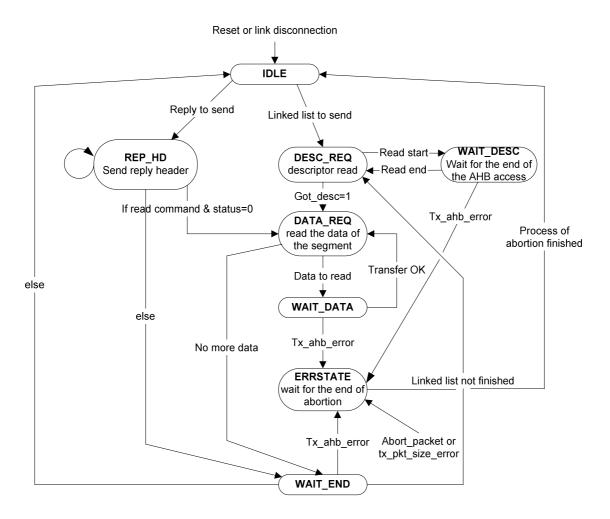

| 8    | .3.4.10 | THI_FSM block                                           | 61 |

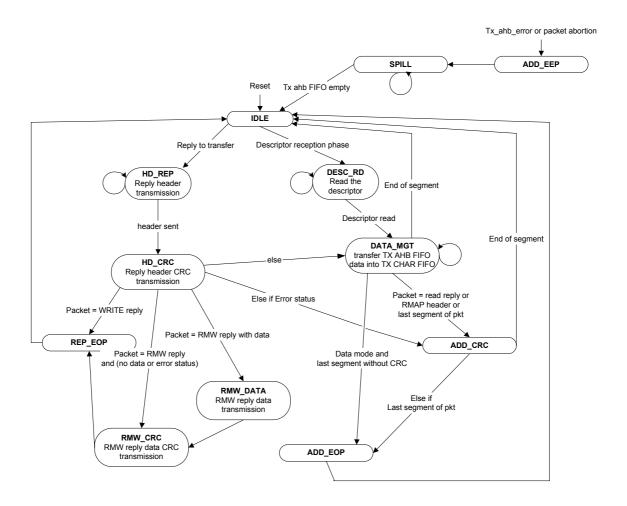

| 8    | .3.4.11 | TX_FIFO_MGT block                                       | 63 |

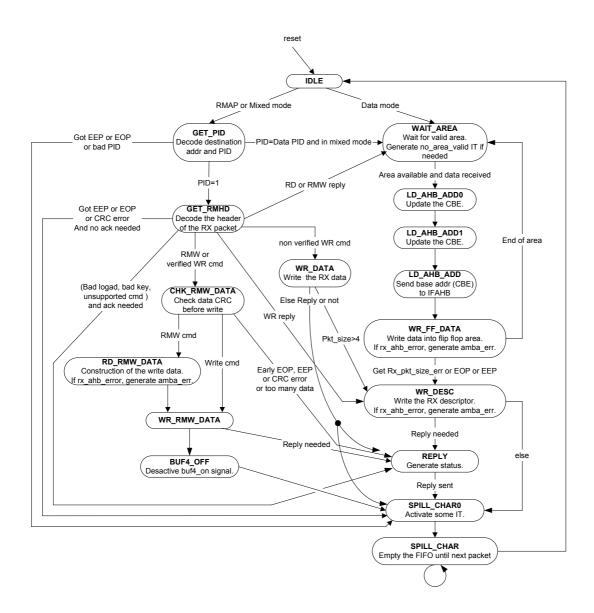

| 8    | .3.4.12 | RX Host Interface [RHI]                                 | 64 |

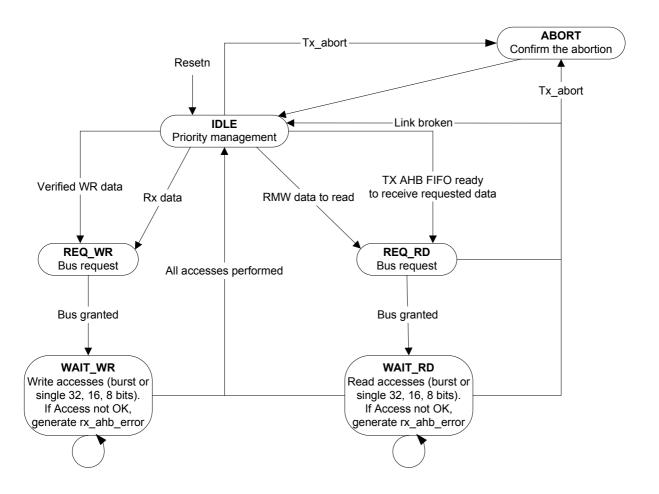

| 8    | .3.4.13 | AHB Interface [IFAHB]                                   | 65 |

| 8    | .3.4.14 | FIFO AHB RX (ahb_fifo_rx) and FIFO_AHB_TX (ahb_fifo_tx) | 65 |

| 8.3. | 5 Block | working at input TX clock                               |    |

| 8    | 351     | CLK TV GEN block                                        | 66 |

Ref : R&D.SCOC3.SP.00626.V.ASTR

Issue : 00 Rev. :05 Date : 2007/10/02

Page: 1

### 1 INTRODUCTION

This document is the specification and architecture of the SPW-RMAP module. This module is part of the SCoC3 design. This document is written in the frame of the ESA R&D "Further development of the Spacecraft Controller on a Chip" reference 20167/06/NL/FM.

Requirements are specified throughout this document in table format as follows:

| Id | Requirement Text | Verification Method | Upper Links |

|----|------------------|---------------------|-------------|

|----|------------------|---------------------|-------------|

- □ The absolute requirement identifier (Id), defined on 4 digits. The first digit corresponds to the current chapter number.

- The requirement text. If tables are considered as part of requirement they are referenced clearly in the text and inserted after and separated from the requirement table and are managed as free text attached to the identifier requirement.

- The verification method (Verif method) as one of the following: R/review of design; I/inspection;

A/analysis; T/test (the paragraph given is from the simulation plan document), S/similarity,

D/definition (not be tracked)

- □ The trace to the upper level requirements (Upper Links), shall be managed with the following format:

- AAAANNNN where AAAA is a label associated to the upper document and NNNN the requirement identifier of this upper level.

- Or **CREATED** key word if the requirement has no link with upper level

All document elements, which are not presented in the table format explained above are not requirements and will not be verified or tracked.

The SPW-RMAP module performs the Spacewire RMAP function.

The Spacewire is a serial high speed link compliant with the ECSS-E-50-12A specification [AD-10].

The RMAP is a protocol built on a spacewire network, compliant with the ECSS-E-50-11 Draft F specification [AD-12].

For the SCOC3 project, the SPW-RMAP block also contains AHB and APB interfaces.

It represents an evolution of the previous ESA/ASTRIUM Spacewire IP Core [AD-11].

It implements improvements of this IP, and the integration of RMAP protocol [AD-12].

The document contains the following sections:

NbCars 69942

Ref: R&D.SCOC3.SP.00626.V.ASTR

Issue : 00 Rev. :05 Date : 2007/10/02

Page: 2

- Applicable and reference documents followed by the list of the acronyms

- A general description of the module in its environment, and of its content

- A detailed description of the module functionality. This section starts by the description of the operating modes of the module. Then all the functions are described

- A description of the registers

- A description of the interfaces

- A detailed description of the architecture

Ref : R&D.SCOC3.SP.00626.V.ASTR

Issue: 00 Rev.:05 Date : 2007/10/02

Page: 3

#### **DOCUMENTS AND ACRONYMS** 2

#### APPLICABLE DOCUMENTS 2.1

| AD-1  | ECSS Q60-02: Final Draft ASIC/FPGA Development Standard,                                                   |

|-------|------------------------------------------------------------------------------------------------------------|

|       | http://www.estec.esa.nl/microelectronics/asic/Final-Draft-ECSS-Q-60-02.pdf                                 |

| AD-2: | VHDL Modelling Guidelines,                                                                                 |

|       | ftp://ftp.estec.esa.nl/pub/vhdl/doc/ModelGuide.pdf                                                         |

| AD-3  | ESA R&D " Further Development of the Spacecraft Controller on a Chip ".Statement of Work                   |

| AD-4  | Telemetry Channel Coding Standard, ESA PSS-04-103, Issue 1, September 1989                                 |

| AD-5  | Telemetry Channel Coding, CCSDS 101.0-B-3, May 1992                                                        |

| AD-6  | Packet Telemetry Standard, ESA PSS-04-106, Issue 1, January 1988                                           |

| AD-7  | Packet Telemetry, CCSDS 102.0-B-4, November 1995                                                           |

| AD-8  | Packet Telecommand Standard, ESA PSS-04-107, Issue 2, April 1992                                           |

| AD-9  | Advanced Microcontroller Bus Architecture (AMBA <sup>TM</sup> ) Specification, revision 2.0, ARM IHI 0011A |

| AD-10 | ESA Spacewire Standard – ECSS-E-50-12A, January 2003                                                       |

| AD-11 | Spacewire IP Core – Specification and Architecture, June 2003                                              |

| AD-12 | Remote Memory Access Protocol – ECSS-E-50-11 Draft F, December 2006                                        |

#### 2.2 REFERENCE DOCUMENTS

| RD-1  | Technical Documentation from Call-Off Order #3 (Spacecraft Controller On-a Chip) of ESA contract #13345/99/NL/FM (Building Blocks for System On-a Chip), known |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | to both parties                                                                                                                                                |

| RD-2: | Contract #13345/99/NL/FM (Building Blocks for System On-a Chip)                                                                                                |

| RD-3  | LEON3 and GRLIB Documentation                                                                                                                                  |

| RD-4  | Synthesisable IP cores available from ESA                                                                                                                      |

| RD-5  | ASIC Design and Manufacturing Requirements, ESA document WDN/PS/700                                                                                            |

| RD-6  | Minutes of informal meeting R&D.SOC.MN.00395.V.ASTR from 15. December 2005, known to both parties                                                              |

Ref : R&D.SCOC3.SP.00626.V.ASTR

Issue: 00 Rev.:05 Date : 2007/10/02

Page: 4

### 2.3 ACRONYMS

| AD        | Applicable Document                               |

|-----------|---------------------------------------------------|

| ADR       | Architectural Design Review                       |

| AIT       | Assembly Integration and Test                     |

| ASIC      | Application Specific Integrated                   |

| 11010     | Circuit                                           |

| ASIM      | Application Specific Integrated                   |

|           | Microsystem                                       |

| ASSP      | Application Specific Standard                     |

|           | Product                                           |

| BLADE     | Board for LEON and Avionics                       |

|           | Development                                       |

| CDR       | Critical Design Review                            |

| CPU       | Central Processor Unit                            |

| DDR       | Detailed Design Review                            |

| DFF       | D-Type Flip Flop                                  |

| DRC       | Design Rule Check                                 |

| DSP       | Digital Signal Processor                          |

| EDAC      | Error Detection And Correction                    |

| EDA       | Electronic Design Automation                      |

| EGSE      | Electrical Ground Support                         |

|           | Equipment                                         |

| ESA       | European Space Agency                             |

| ESTEC     | European Space Research and                       |

|           | Technology Centre                                 |

| FDIR      | Failure Detection Isolation and                   |

| ED C 4    | Recovery                                          |

| FPGA      | Field Programmable Gate Array                     |

| GEO       | Geosynchronous Equatorial Orbit                   |

| GRLIB     | Gaisler Research Library,                         |

| HDL       | Hardware Description Language                     |

| I/O       | Input/Output                                      |

| ID<br>IDR | Identification                                    |

| IEEE      | Initial Design Review Institute of Electrical and |

| TEEE      | Electronics Engineers                             |

| IP, IPR   | Intellectual Property, Intellectual               |

| 11,111    | Property Rights                                   |

| IPMON     | Performance Monitoring (IP                        |

| II MOIV   | block)                                            |

| ITT       | Invitation To Tender                              |

| JTAG      | Joint Test Action Group (refer to                 |

| J =       | IEEE std 1149.1)                                  |

| LEO       | Low Earth Orbit                                   |

| LET       | Linear Energy Transfer                            |

| OBDH      | On Board Data Handling                            |

| OBMU      | On Board Management Unit                          |

| PCB       | Printed Circuit Board                             |

| r CD      | Finited Circuit Doard                             |

| PDF   | Portable Document Format           |

|-------|------------------------------------|

| PDR   | Preliminary Design Review          |

| PM    | Performance Monitoring (in fact    |

|       | called IPMON)                      |

| PM    | Processor Module                   |

| RD    | Reference Document                 |

| RTEMS |                                    |

| RTOS  | Real Time Operating System         |

|       | (example: RTEMS)                   |

| SOC   | System On a Chip                   |

| SCoC  | Spacecraft Controller on a Chip    |

| SEE   | Single Event Effect (or SEP Single |

|       | Event Phenomena)                   |

| SEL   | Single Event Latch up              |

| SEP   | see SEE                            |

| SET   | Single Event Transient             |

| SEU   | Single Event Upset                 |

| SRAM  | Static Random Access Memory        |

| SRR   | Specification Requirement Review   |

| TC    | TeleCommand                        |

| TID   | Total Integrated Dose              |

| TM    | TeleMetry                          |

| TRP   | Technological Research             |

|       | Programme                          |

| VHDL  | VHSIC Hardware Description         |

|       | Language,                          |

| VLSI  | Very Large Scale Integration       |

| WP    | Work Package                       |

| WWW   | World Wide Web                     |

Ref: R&D.SCOC3.SP.00626.V.ASTR

Issue : 00 Rev. :05 Date : 2007/10/02

Page: 5

### 3 GENERAL DESCRIPTION OF THE MODULE

|   |      | The SPW-RMAP shall be a high-speed serial link to transmit and receive packets of data [AD-10]. | D    | CREATED |

|---|------|-------------------------------------------------------------------------------------------------|------|---------|

| ſ |      |                                                                                                 |      |         |

|   | 3010 | The SPW-RMAP shall support RMAP protocol [AD-12].                                               | 4.13 | CREATED |

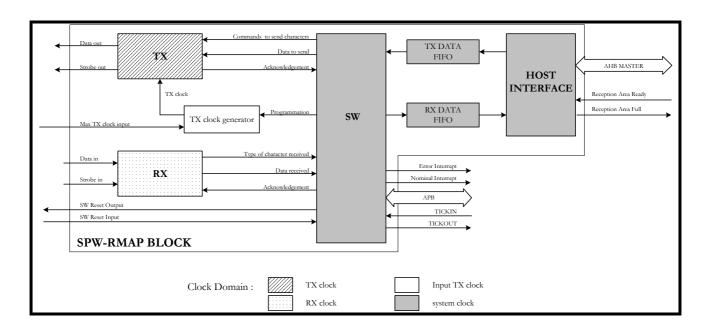

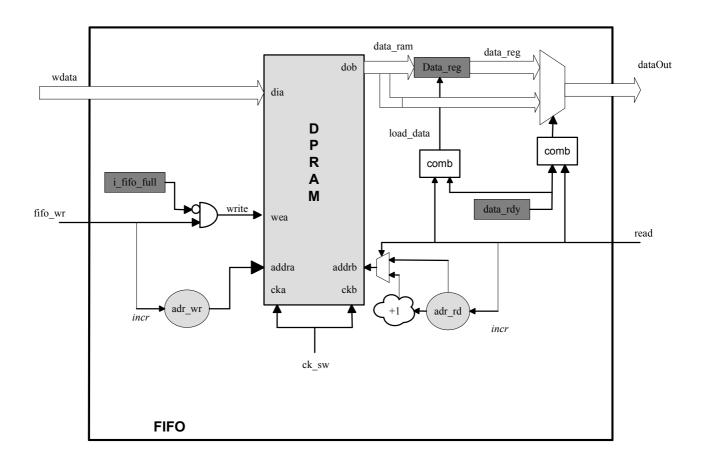

Figure 1: SPW-RMAP General Architecture

| 3020 | The SPW-RMAP shall implement general architecture given in Figure 1.                 | D    | CREATED  |

|------|--------------------------------------------------------------------------------------|------|----------|

|      |                                                                                      |      |          |

| 3030 | The Host Interface block shall be an interface with the AMBA AHB and APB             | 4.4  | CREATED  |

|      | buses.                                                                               | 4.5  |          |

|      | It shall contain the management of the data sent by the host application.            | 4.7  |          |

|      | It shall manage the storage of data into the host memory.                            | 4.13 |          |

|      | All RMAP specificities shall be implemented in this block.                           |      |          |

|      |                                                                                      |      | <u> </u> |

| 3040 | The TX Data FIFO block shall be a 9-bits FIFO containing the data to be transmitted. | D    | CREATED  |

NbCars 69942

NbWords 13939 FileName Spec\_Archi\_RMAP\_rev05.doc

Ref : R&D.SCOC3.SP.00626.V.ASTR

Issue: 00 Rev.:05 Date : 2007/10/02

Page: 6

| 3050 | The RX Data FIFO block shall be a 9-bits FIFO containing the data to be stored into the host memory. | D     | CREATED |

|------|------------------------------------------------------------------------------------------------------|-------|---------|

|      |                                                                                                      |       |         |

| 3060 | The SW block shall manage the initialisation protocol.                                               | 4.12  | CREATED |

|      | This block shall select the character to be transmitted and check any error                          |       |         |

|      | occurrence.                                                                                          |       |         |

|      |                                                                                                      |       |         |

| 3070 | The TX block shall send the character at the transmission frequency.                                 | I     | CREATED |

|      |                                                                                                      |       |         |

| 3080 | The RX block shall identify the received character type.                                             | 4.12  | CREATED |

|      |                                                                                                      | 4.4.1 |         |

|      |                                                                                                      |       |         |

| 3090 | The TX clock generator block shall generate the clock transmission rate.                             | D     | CREATED |

Ref: R&D.SCOC3.SP.00626.V.ASTR

Issue : 00 Rev. :05 Date : 2007/10/02

Page: 7

### 4 DETAILED DESCRIPTION OF THE MODULE FUNCTIONALITY

### 4.1 **OPERATING MODES**

| 4000 | The SPW-RMAP shall support the following operating modes:                                                                               | D | CREATED |

|------|-----------------------------------------------------------------------------------------------------------------------------------------|---|---------|

|      | • RESET mode (resetn=0):                                                                                                                |   |         |

|      | TX and RX blocks shall be inactive                                                                                                      |   |         |

|      | Host interface shall be inactive                                                                                                        |   |         |

|      | • ACTIVE mode (resetn=1):                                                                                                               |   |         |

|      | TX block shall be inactive and RX block shall be active (when entering the ACTIVE mode)                                                 |   |         |