Ref: R&D.SCOC3.RP.00539.V.ASTR

Issue : 03 Rev. :00 Date : 2008/05/05

Page: i

#### ESA R&D n° 20167/06/NL/FM

### Further Development of the Spacecraft Controller on a Chip

# IPMON module Specification and architecture definition

|               | Name and Function                                  | Date       | Signature |

|---------------|----------------------------------------------------|------------|-----------|

| Prepared by   | <b>Aurélien LEFEVRE</b><br>Digital design engineer | 05/05/2008 |           |

| Verified by   | <b>Marc SOUYRI</b><br>ASIC expert                  | 15/05/2008 | Cenony    |

| Authorized by | Franck KOEBEL<br>SCOC3 Asic Responsible            | 16/05/2008 | T. Wall   |

| Document type | Nb WBS | Keywords |

|---------------|--------|----------|

|               |        |          |

Ref : R&D.SCOC3.RP.00539.V.ASTR

Issue : 03 Rev. :00 Date : 2008/05/05

Page : ii

### **DOCUMENT CHANGE LOG**

| Issue/<br>Revision | Date     | Modification Nb | Modified pages | Observations                                                                                                                         |

|--------------------|----------|-----------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------|

| 00/00              | 07/02/28 |                 |                |                                                                                                                                      |

| 01/00              | 07/03/14 |                 |                | Added architecture.                                                                                                                  |

| 01/01              | 07/03/21 |                 |                | Architecture modification.                                                                                                           |

| 02/00              | 07/06/05 |                 |                | Modification of the trigger function. Added generics to configure IPMON.                                                             |

| 02/01              | 07/07/25 |                 |                | Changed generics by constants. Update after coding and simulation.                                                                   |

| 02/02              | 07/12/20 |                 |                | - Added a generic defining<br>the index of IPMON on<br>AHB bus.                                                                      |

|                    |          |                 |                | - Fixed typos.                                                                                                                       |

|                    |          |                 |                | - Added requirements 5065<br>and 5093 to mask<br>accesses from TCDD<br>master to ATC PROM<br>slave for both trace and<br>statistics. |

| 02/03              | 08/01/30 |                 |                | Corrected registers label and registers description order in § 6.                                                                    |

NbCars

38578

NbWords

7475

FileName

IPMON\_SPEC\_ARCHI\_103\_R00.doc

© EADS/Astrium

Ref : R&D.SCOC3.RP.00539.V.ASTR

Issue : 03 Rev. :00 Date : 2008/05/05

Page : iii

| 03/00 | 08/04/15 |  | - Added new functionalities (trace buffer counter, statistics buffer initialization, enable conditional start, idle mode, trig condition on Wait States and Grant delays).                                                                                    |

|-------|----------|--|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |          |  | <ul> <li>Changed the width of<br/>internal registers, trace<br/>word and statistics word<br/>fields.</li> </ul>                                                                                                                                               |

|       |          |  | - Clarified some points of specification (first and last accesses included in trace/statistics in case of conditional trig, difference between it_error and it_cnt_ovflow and associated behaviour, definition of split time and of lock time, block diagram) |

|       |          |  | - Added asynchronous reset and output values at reset                                                                                                                                                                                                         |

Ref : R&D.SCOC3.RP.00539.V.ASTR

Issue: 03 Rev. :00 Date : 2008/05/05

$\hbox{Page} \ : \ iv$

### PAGE ISSUE RECORD

Issue of this document comprises the following pages at the issue shown

| Issue/<br>Rev. | Page | Issue/<br>Rev. | Page      | Issue/<br>Rev. | Page           | Issue/<br>Rev. | Page                | Issue/<br>Rev.           | Page                          | Issue/<br>Rev.                |

|----------------|------|----------------|-----------|----------------|----------------|----------------|---------------------|--------------------------|-------------------------------|-------------------------------|

| 03/00          |      |                |           |                |                |                |                     |                          |                               |                               |

|                |      |                |           |                |                |                |                     |                          |                               |                               |

|                |      |                |           |                |                |                |                     |                          |                               |                               |

|                |      |                |           |                |                |                |                     |                          |                               |                               |

|                |      |                |           |                |                |                |                     |                          |                               |                               |

|                |      |                |           |                |                |                |                     |                          |                               |                               |

|                |      |                |           |                |                |                |                     |                          |                               |                               |

|                |      |                |           |                |                |                |                     |                          |                               |                               |

|                |      |                |           |                |                |                |                     |                          |                               |                               |

|                |      |                |           |                |                |                |                     |                          |                               |                               |

|                |      |                |           |                |                |                |                     |                          |                               |                               |

|                |      |                |           |                |                |                |                     |                          |                               |                               |

|                |      |                |           |                |                |                |                     |                          |                               |                               |

|                | Rev. | Rev.           | Rev. Rev. | Rev. Rev.      | Rev. Rev. Rev. | Rev. Rev. Rev. | Rev. Rev. Rev. Rev. | Rev. Rev. Rev. Rev. Rev. | Rev. Rev. Rev. Rev. Rev. Rev. | Rev. Rev. Rev. Rev. Rev. Rev. |

NbCars NbWords FileName 38578

7475 IPMON\_SPEC\_ARCHI\_I03\_R00.doc

Ref : R&D.SCOC3.RP.00539.V.ASTR

Issue: 03 Rev. :00 Date : 2008/05/05

Page: v

#### **TABLE OF CONTENTS**

| 1   | INTRODUCTION                            |    |

|-----|-----------------------------------------|----|

| 2   | DOCUMENTS AND ACRONYMS                  | 2  |

| 2.1 | APPLICABLE DOCUMENTS                    | 2  |

| 2.2 | REFERENCE DOCUMENTS                     | 2  |

| 2.3 | ACRONYMS                                | 3  |

| 3   | GENERAL DESCRIPTION OF THE MODULE       | 5  |

| 4   | GENERAL REQUIREMENTS                    | 5  |

| 5   | SPECIFIC REQUIREMENTS OF FUNCTIONNALITY | 6  |

| 5.1 | AHB SLAVE INTERFACE                     | 6  |

| 5.2 | APB interface                           | 6  |

| 5.3 | Trace Function                          | 6  |

| 5.4 | STATISTIC FUNCTION                      | 8  |

| 5.5 | Trigger function                        | 12 |

| 5.6 | INTERRUPT FUNCTION                      | 14 |

| 6   | REGISTERS DEFINITION                    | 15 |

| 7   | CONFIGURATION OPTIONS                   | 25 |

| 8   | INTERFACES                              | 27 |

| 9   | ARCHITECTURE DESCRIPTION                | 31 |

| 9.1 | STATISTICS BLOCK DESCRIPTION            | 32 |

| 9.2 | TRACE BLOCK DESCRIPTION                 | 34 |

| 9.3 | MEMORY BLOCK DESCRIPTION                | 35 |

| 9.4 | APB INTERFACE DESCRIPTION               | 36 |

| 9.5 | AHB INTERFACE DESCRIPTION               | 37 |

| 9.6 | Trigger block description               | 39 |

| 10  | TESTABILITY                             | 41 |

| 11  | SEU PROTECTION                          | 41 |

Ref: R&D.SCOC3.RP.00539.V.ASTR

Issue : 03 Rev. :00 Date : 2008/05/05

Page: 1

#### 1 INTRODUCTION

This document is the specification of the IPMON module. This module is part of the SCoC3 design. This document is written in the frame of the ESA R&D "Further development of the Spacecraft Controller on a Chip" reference 20167/06/NL/FM.

Requirements are specified throughout this document in table format as follows:

| Id | Requirement Text | Verification Method | Upper Links |

|----|------------------|---------------------|-------------|

|----|------------------|---------------------|-------------|

- the absolute requirement identifier (Id), defined on 4 digits. The first digit corresponds to the current chapter number.

- the requirement text. If tables are considered as part of the requirement, they are referenced clearly in the text, inserted after and separated from the requirement table, and are managed as free text attached to the identifier requirement.

- the verification method as one of the following: R/review of design; I/inspection; A/analysis; T/test, S/similarity, D/definition (not be tracked).

- the trace to the upper level requirements (Upper Links), shall be managed with the following format:

- **AAAANNNN** where AAAA is a label associated to the upper document and NNNN the requirement identifier of this upper level.

- Or CREATED key word if the requirement has no link with upper level

All document elements, which are not presented in the table format explained above, are not requirements and will not be verified or tracked.

The IPMON module shall perform monitoring on AHB bus.

The document contains the following sections:

- Applicable and reference documents followed by the list of acronyms

- A general description of the module in its environment, and of its content

- A description of the module requirements. This section starts with general requirements, followed by specific requirements of functionality.

- A description of the interfaces

- A detailed description of the architecture

NbWords 7475

FileName IPMON SPEC ARCHI I03 R00.doc

Ref : R&D.SCOC3.RP.00539.V.ASTR

Issue: 03 Rev. :00 Date : 2008/05/05

Page: 2

#### 2 **DOCUMENTS AND ACRONYMS**

#### APPLICABLE DOCUMENTS 2.1

| AD-1 | ECSS Q60-02A: Space Product Assurance – ASIC and FPGA Development Standard (17 July 2007)                  |

|------|------------------------------------------------------------------------------------------------------------|

| AD-2 | VHDL Modelling Guidelines,                                                                                 |

|      | ftp://ftp.estec.esa.nl/pub/vhdl/doc/ModelGuide.pdf                                                         |

| AD-3 | ESA R&D "Further Development of the Spacecraft Controller on a Chip". Statement of Work                    |

| AD-4 | Advanced Microcontroller Bus Architecture (AMBA <sup>TM</sup> ) Specification, revision 2.0, ARM IHI 0011A |

#### 2.2 REFERENCE DOCUMENTS

| RD-1 | Technical Documentation from Call-Off Order #3 (Spacecraft Controller On-a Chip) of ESA contract #13345/99/NL/FM (Building Blocks for System On-a Chip), known to both parties |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RD-2 | Contract #13345/99/NL/FM (Building Blocks for System On-a Chip)                                                                                                                |

| RD-3 | LEON3 and GRLIB Documentation v1.0.15 April, 2007                                                                                                                              |

| RD-4 | Synthesisable IP cores available from ESA                                                                                                                                      |

| RD-5 | ASIC Design and Manufacturing Requirements, ESA document WDN/PS/700                                                                                                            |

| RD-6 | Minutes of informal meeting R&D.SOC.MN.00395.V.ASTR from 15. December 2005, known to both parties                                                                              |

| RD-7 | Inputs for Improvement of Prosilogs AHB Monitor Tool (M. Carlqvist, R. Weigand) Issue 1, Revision 0 Draft.                                                                     |

NbCars NbWords FileName 38578 7475 IPMON\_SPEC\_ARCHI\_I03\_R00.doc

Ref : R&D.SCOC3.RP.00539.V.ASTR

Issue: 03 Rev. :00 Date : 2008/05/05

Page: 3

#### 2.3 **ACRONYMS**

| AD         | A = -1:1-1- D =                     |

|------------|-------------------------------------|

| ADD        | Applicable Document                 |

| ADR        | Architectural Design Review         |

| AIT        | Assembly Integration and Test       |

| AHB        | AMBA High speed Bus                 |

| AMBA       | Advanced Microcontroller Bus        |

|            | Architecture                        |

| ASIC       | Application Specific Integrated     |

|            | Circuit                             |

| ASIM       | Application Specific Integrated     |

|            | Microsystem                         |

| ASSP       | Application Specific Standard       |

|            | Product                             |

| BLADE      | Board for LEON and Avionics         |

|            | DEvelopment                         |

| CDR        | Critical Design Review              |

| CPU        | Central Processor Unit              |

| DDR        | Detailed Design Review              |

| DFF        | D-Type Flip Flop                    |

| DRC        | Design Rule Check                   |

| DSP        | Digital Signal Processor            |

| EDAC       | Error Detection And Correction      |

| EDA        | Electronic Design Automation        |

| EGSE       | Electrical Ground Support           |

| LOSE       | Equipment                           |

| ESA        | European Space Agency               |

| ESTEC      | European Space Research and         |

| ESTEC      | Technology Centre                   |

| FDIR       | Failure Detection Isolation and     |

| IDIK       | Recovery                            |

| FPGA       | Field Programmable Gate Array       |

| GEO        | Geosynchronous Equatorial Orbit     |

| GRLIB      |                                     |

|            | Gaisler Research Library,           |

| HDL<br>L/O | Hardware Description Language       |

| I/O        | Input/Output Identification         |

| ID         | Tuellane au an                      |

| IDR        | Initial Design Review               |

| IEEE       | Institute of Electrical and         |

| ID IDE     | Electronics Engineers               |

| IP, IPR    | Intellectual Property, Intellectual |

| IDMON      | Property Rights                     |

| IPMON      | Performance Monitoring (IP          |

| T/T//T     | block)                              |

| ITT        | Invitation To Tender                |

| JTAG       | Joint Test Action Group (refer to   |

| 170        | IEEE std 1149.1)                    |

| LEO        | Low Earth Orbit                     |

| LET        | Linear Energy Transfer              |

| OBDH  | On Board Data Handling             |

|-------|------------------------------------|

| OBMU  | On Board Management Unit           |

| PCB   | Printed Circuit Board              |

| PDF   | Portable Document Format           |

| PDR   | Preliminary Design Review          |

| PM    | Performance Monitoring (in fact    |

|       | called IPMON)                      |

| PM    | Processor Module                   |

| RD    | Reference Document                 |

| RTEMS |                                    |

| RTOS  | Real Time Operating System         |

|       | (example: RTEMS)                   |

| SOC   | System On a Chip                   |

| SCoC  | Spacecraft Controller on a Chip    |

| SEE   | Single Event Effect (or SEP Single |

|       | Event Phenomena)                   |

| SEL   | Single Event Latch up              |

| SEP   | see SEE                            |

| SET   | Single Event Transient             |

| SEU   | Single Event Upset                 |

| SRAM  | Static Random Access Memory        |

| SRR   | Specification Requirement Review   |

| TC    | TeleCommand                        |

| TID   | Total Integrated Dose              |

| TM    | TeleMetry                          |

| TRP   | Technological Research             |

|       | Programme                          |

| VHDL  | VHSIC Hardware Description         |

|       | Language,                          |

| VLSI  | Very Large Scale Integration       |

| WP    | Work Package                       |

| WWW   | World Wide Web                     |

NbCars

38578

NbWords

7475

FileName

IPMON\_SPEC\_ARCHI\_103\_R00.doc

Ref : R&D.SCOC3.RP.00539.V.ASTR

Issue : 03 Rev. :00 Date : 2008/05/05

Page: 5

#### 3 GENERAL DESCRIPTION OF THE MODULE

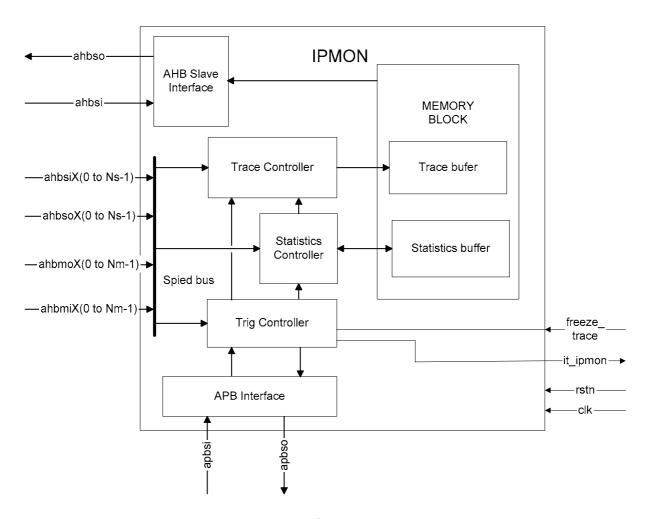

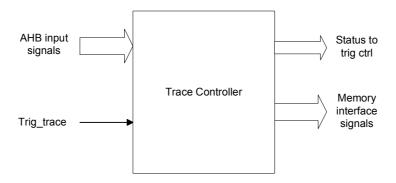

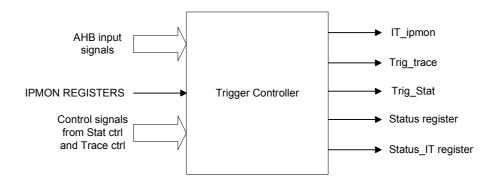

The IP Monitoring (IPMON) module is used to spy an AHB Bus, recording trace and statistics data. This IP is designed in the context of the SCOC3 project but can be used as a generic AHB spy module.

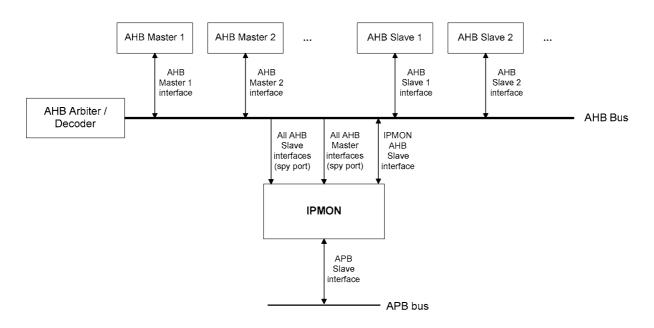

The IPMON is used on an AHB bus (Figure 1):

Figure 1 – IPMON on AHB environment

#### 4 GENERAL REQUIREMENTS

| 4000 | The IPMON shall spy the AHB bus.                                                |  |

|------|---------------------------------------------------------------------------------|--|

|      |                                                                                 |  |

| 4010 | The IPMON shall implement an AHB slave interface.                               |  |

|      |                                                                                 |  |

| 4020 | The IPMON shall integrate a Statistics block.                                   |  |

|      |                                                                                 |  |

| 4030 | The IPMON shall integrate a Trace block inspired by the DSU philosophy [RD3].   |  |

|      |                                                                                 |  |

| 4040 | The IPMON shall have configurable trigger conditions to launch statistics block |  |

NbCars 38578

NbWords 7475 FileName IPMON\_SPEC\_ARCHI\_I03\_R00.doc

Ref : R&D.SCOC3.RP.00539.V.ASTR

Issue: 03 Rev. :00 Date : 2008/05/05

Page: 6

|            | and/or trace block.                                                                                                                              |   |  |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------|---|--|

|            |                                                                                                                                                  |   |  |

| 4050       | The IPMON shall have internal memory blocks to save trace and statistics data.                                                                   |   |  |

|            |                                                                                                                                                  |   |  |

| 4060       | The IPMON shall manage from 1 to 16 masters and from 1 to 16 slaves for trace and statistics (configurable using constants).                     |   |  |

|            |                                                                                                                                                  |   |  |

| 4070       | The IPMON shall manage only 32-bit word size when accessed on its AHB slave interface.                                                           |   |  |

|            |                                                                                                                                                  |   |  |

|            |                                                                                                                                                  |   |  |

| 5 S        | PECIFIC REQUIREMENTS OF FUNCTIONNALITY                                                                                                           |   |  |

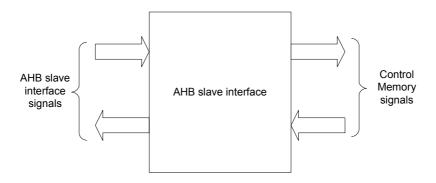

| 5.1        | AHB SLAVE INTERFACE                                                                                                                              |   |  |

| 5000       | Deleted.                                                                                                                                         |   |  |

|            |                                                                                                                                                  |   |  |

| 5010       | The AHB slave interface shall be used to read all trace and statistics data contained in the Trace buffer and in the Statistics buffer.          |   |  |

|            |                                                                                                                                                  |   |  |

| <b>5</b> 0 | ADD INTERESTOR                                                                                                                                   |   |  |

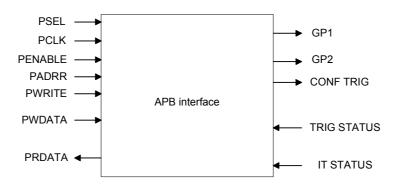

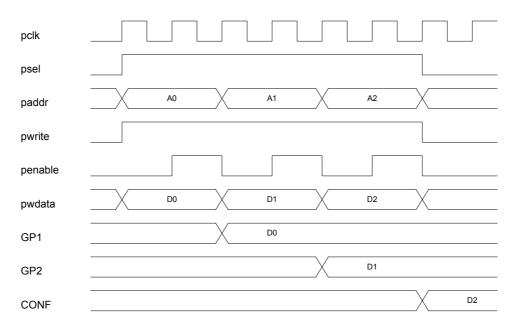

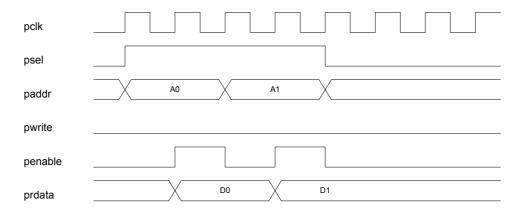

| 5.2        | APB INTERFACE                                                                                                                                    |   |  |

| 5020       | The IPMON shall implement an APB slave interface.                                                                                                |   |  |

|            |                                                                                                                                                  |   |  |

| 5030       | The APB interface shall be used to configure the IPMON registers.                                                                                |   |  |

|            |                                                                                                                                                  |   |  |

|            |                                                                                                                                                  |   |  |

| 5.3        | TRACE FUNCTION                                                                                                                                   |   |  |

|            |                                                                                                                                                  |   |  |

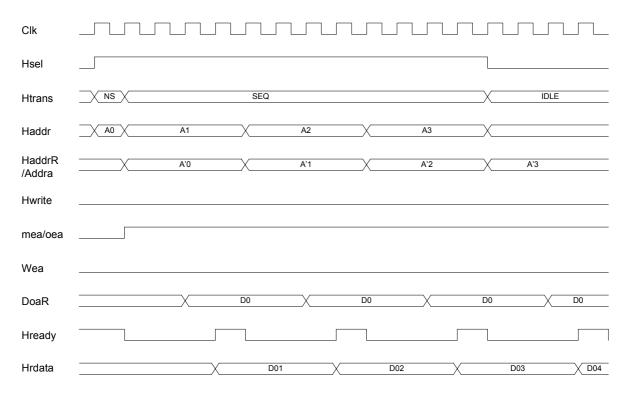

| 5040       | The IPMON shall integrate a Trace function used to record the traffic on the AHB bus. 'NON-SEQ' and 'SEQ' AHB transfers shall be traced, whereas | Ī |  |

|            | 'IDLE' or 'BUSY' transfers shall not be traced.                                                                                                  | i |  |

NbCars NbWords FileName 38578 7475 IPMON\_SPEC\_ARCHI\_103\_R00.doc

Ref : R&D.SCOC3.RP.00539.V.ASTR

Issue : 03 Rev. :00 Date : 2008/05/05

Page: 7

| 5050 | The Trace function shall start and end recording the traffic according to the Trigger function control.                                           |  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 5060 | The IPMON shall integrate an AHB trace buffer inspired by the DSU function [RD3].                                                                 |  |

|      |                                                                                                                                                   |  |

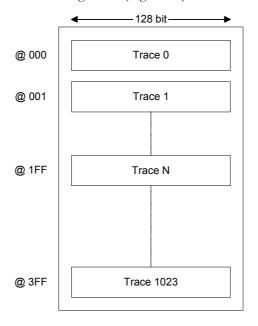

| 5061 | The IPMON AHB trace buffer shall use a dedicated memory of between 64 and 1024 words of 128 bits (number of words configurable using a constant). |  |

|      |                                                                                                                                                   |  |

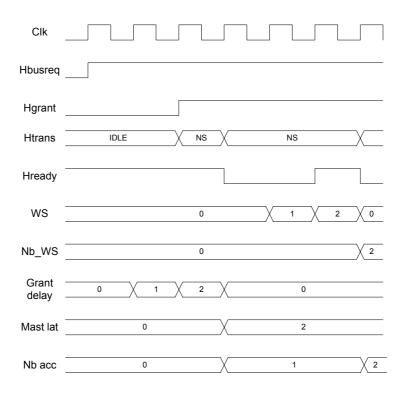

| 5062 | The 128-bit trace word shall be organized as depicted in Figure 2.                                                                                |  |

| Bits  | Field Name        | Description                                                                                            |

|-------|-------------------|--------------------------------------------------------------------------------------------------------|

| 12798 | Time tag          | Trace time counter (reset at the beginning of each trace function activation)                          |

| 9787  | Grant delay       | Delay between Hbusreq = '1' and Hgrant = '1'                                                           |

| 8678  | Wait states       | Number of wait states (Hready low)                                                                     |

| 77    | Hwrite            | AHB Hwrite value                                                                                       |

| 76    | Htrans(0)         | LSB of AHB Htrans value ('0' for NON-SEQ accesses, '1' for SEQ accesses)                               |

| 7574  | Hsize(1 downto 0) | LSBs of AHB Hsize value ("00" for 8-bit accesses, "01" for 16-bit accesses, "10" for 32-bit accesses). |

| 7371  | Hburst            | AHB Hburst value                                                                                       |

| 7067  | Hmaster           | AHB Hmaster value                                                                                      |

| 66    | Hmastlock         | AHB Hmastlock value                                                                                    |

| 6564  | Hresp             | AHB Hresp value                                                                                        |

| 6332  | Data              | AHB HRDATA or HWDATA value                                                                             |

| 310   | Haddr             | AHB HADDR value                                                                                        |

Figure 2: 128-bit trace word arrangement

| 5063 | The internal register used to count the number of Wait States shall be 9-bit wide.                                                   |  |

|------|--------------------------------------------------------------------------------------------------------------------------------------|--|

|      | The internal registers used to count the Grant Delays shall be 11-bit wide.                                                          |  |

|      | The width of the internal register used to count the split time shall be configurable using a constant (SCOC3 default value: 1 bit). |  |

NbCars

38578

NbWords

7475

FileName

IPMON\_SPEC\_ARCHI\_103\_R00.doc

Ref : R&D.SCOC3.RP.00539.V.ASTR

Issue : 03 Rev. :00 Date : 2008/05/05

Page: 8

The Trace function shall generate two interrupts to the IPMON Interrupt function in case of the following events:

- The Trace function stopped due to Freeze\_trace pin activation.

- The Trace function stopped.

In the SCOC3 project, the IPMON shall not record traces for accesses between TCDD master and its prom memory (ATC).

- This function can be enabled or not (for other projects) using a constant.

- The TCDD master number on the AHB bus is given to the IPMON by a generic.

- The ATC prom memory mapping is (constants in IPMON package):

- $\circ$  START\_ADD = 0x0040\_0000

- $\circ$  END\_ADD = 0x0082\_FFFF

Each time the trace function is activated, the index of the trace buffer shall restart at address 0. When more than 1024 128-bit words are written in the trace buffer, a roll over shall occur. The 'TR\_BUF\_CNT' field of the Trace Status Register shall indicate the number of words written in the trace buffer and whether a roll over occurred or not.

#### 5.4 STATISTIC FUNCTION

5070 Deleted.

The statistics block shall compute the following statistics for each master/slave pair:

- Cumulated number of errors

- Cumulated number of OK,

- Cumulated number of split,

- Cumulated number of retries,

- Cumulated number of wait states,

- Cumulated latency for the master (Grant delay),

NbCars 38578 NbWords 7475

FileName IPMON\_SPEC\_ARCHI\_I03\_R00.doc

Ref : R&D.SCOC3.RP.00539.V.ASTR

Issue: 03 Rev.:00 Date : 2008/05/05

Page: 9

Cumulated number of accesses (SEQ and NON-SEQ),

- Cumulated lock time,

- Cumulated split time,

- Cumulated lock numbers.

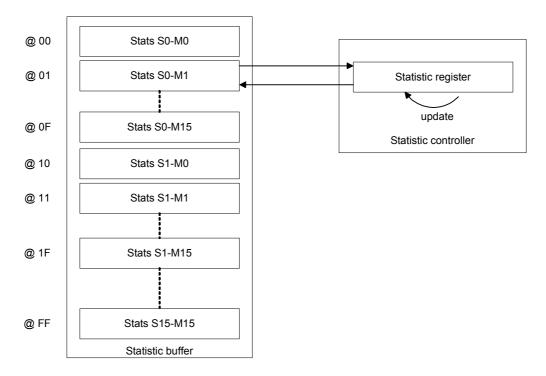

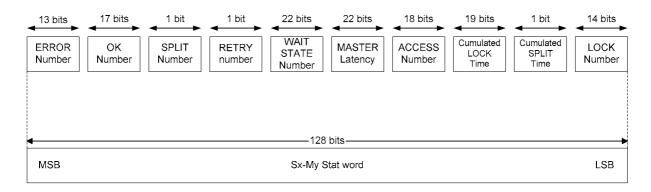

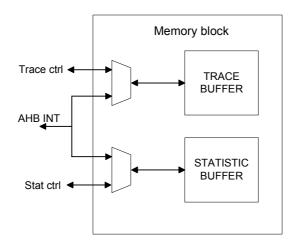

5081 The statistics for a master/slave pair shall be stored in a data word organized as depicted in Figure 3.

| Bits | Field Name            | Description                                                                           |  |

|------|-----------------------|---------------------------------------------------------------------------------------|--|

| MSBs | ERROR number          | Cumulated number of ERROR responses (field size = NBITS_ERROR_REG bits)               |  |

|      | OKAY number           | Cumulated number of OKAY responses (field size = NBITS_OKAY_REG bits)                 |  |

|      | Split number          | Cumulated number of SPLIT responses (field size = NBITS_SPLIT_REG bits)               |  |

|      | Retry number          | Cumulated number of RETRY responses (field size = NBITS_RETRY_REG bits)               |  |

|      | Wait states<br>number | Cumulated number of wait states (field size = NBITS_WS_REG bits)                      |  |

|      | Master latency        | Cumulated latency for the master (Grant delay) (field size = NBITS_MAST_LAT_REG bits) |  |

|      | Access number         | Cumulated number of accesses (SEQ and NON-SEQ) (field size = NBITS_NB_ACC_REG bits)   |  |

|      | Cumulated lock time   | Cumulated lock time (field size = NBITS_LOCK_DELAY_REG bits)                          |  |

|      | Cumulated split time  | Cumulated split time (field size = NBITS_SPLIT_DELAY_REG bits)                        |  |

| LSBs | Lock number           | Cumulated number of locks (field size = NBITS_NB_LOCK_REG bits)                       |  |

Figure 3: 128-bit statistic word arrangement

The number of bits of each field of the 128-bit statistic word is configurable using constants (refer to section 7). The total number of bits of these 10 fields shall be exactly equal to 128. The user who customizes these values is in charge of verifying this rule.

| 5082 | The statistics data words shall be stored in memory in a dedicated statistics |  |  |

|------|-------------------------------------------------------------------------------|--|--|

|      | Buffer. The buffer size depends on the number of masters and slaves on the    |  |  |

|      | AHB bus. This size is between 1 (for 1 master/slave pair) and 256 (for 16     |  |  |

|      | masters and 16 slaves) words of 128 bits. The address in this buffer shall be |  |  |

NbCars NbWords FileName

Ref : R&D.SCOC3.RP.00539.V.ASTR

Issue: 03 Rev. :00 Date : 2008/05/05

Page : 10

|      | calculated by appending the slave number (4 bits) and the master number (4 bits).                                                                                                                                                                                                                                                                                                   |  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 5083 | The statistics buffer shall be automatically initialized at the end of each soft reset.                                                                                                                                                                                                                                                                                             |  |

| 5084 | The user shall be able to trigger the initialization of the statistics buffer by writing the INIT_STAT_BUFFER field in the Control Register.                                                                                                                                                                                                                                        |  |

| 5085 | During the initialization of the statistics buffer (as indicated by the value of the INIT_STAT_BUFFER field of the Control Register), no other functionalities of the IPMON shall be usable:  - it shall not be possible to activate trace and statistics functions  - the IPMON AHB slave interface shall answer HRESP=ERROR responses                                             |  |

| 5086 | When the statistics function is activated multiple times without initializing the statistics buffer, the statistics shall be cumulated.                                                                                                                                                                                                                                             |  |

| 5090 | The IPMON shall perform the statistics during a programmable maximum integration time.                                                                                                                                                                                                                                                                                              |  |

| 5091 | The programmable maximum integration time shall be configurable through the APB bus by using the IPMON Statistic Delay Register, as defined in section 6.                                                                                                                                                                                                                           |  |

| 5092 | The Statistic function shall generate two interrupts to the IPMON Interrupt function in case of the following events:  • One of the 10 registers composing the statistics word reached its maximum value (in case one of these registers tries to overflow, no roll over shall occur and the register shall be saturated to its maximum value).  • The statistics function stopped. |  |

NbCars NbWords FileName

38578 7475 IPMON\_SPEC\_ARCHI\_I03\_R00.doc

Ref : R&D.SCOC3.RP.00539.V.ASTR

Issue: 03 Rev.:00 Date : 2008/05/05

Page : 11

5093 In the SCOC3 project, the IPMON shall not record statistics for accesses between TCDD master and its prom memory (ATC).

- This function can be enabled or not (for other projects) using a constant.

- The TCDD master number on the AHB bus is given to the IPMON by a generic.

- The ATC prom memory mapping is (constant in IPMON package):

- $\circ \quad START\_ADD = 0x0040\_0000$

- $\circ$  END\_ADD = 0x0082\_FFFF

NbWords FileName

7475 IPMON\_SPEC\_ARCHI\_I03\_R00.doc

Ref : R&D.SCOC3.RP.00539.V.ASTR

Issue: 03 Rev. :00 Date : 2008/05/05

Page : 12

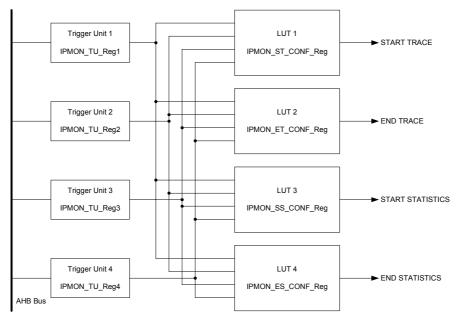

| 5100 | The IPMON shall integrate a trigger function used to control the activation of the Trace and Statistics functions.                                                                                                                                                             |      |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|      |                                                                                                                                                                                                                                                                                |      |

| 5101 | There shall be two ways to start and stop Trace and Statistics functions:                                                                                                                                                                                                      |      |

|      | • unconditionally, writing the APB_TRIG Register: The trig order (start or stop Trace or Statistics function) shall be immediately executed                                                                                                                                    |      |

|      | • conditionally, using 'Trigger Units': it shall be possible to program Trace or Statistics functions to be triggered when a specific transfer occurs on the bus                                                                                                               |      |

|      |                                                                                                                                                                                                                                                                                |      |

| 5110 | The Trigger function shall implement the following trigger conditions for the Trace and statistics functions:                                                                                                                                                                  |      |

|      | Trig on Wait States/Grant delay value                                                                                                                                                                                                                                          |      |

|      | Trig on address/data value,                                                                                                                                                                                                                                                    |      |

|      | • Trig on HRESP value,                                                                                                                                                                                                                                                         |      |

|      | • Trig on HWRITE value,                                                                                                                                                                                                                                                        |      |

|      | Trig on HSLAVE number,                                                                                                                                                                                                                                                         |      |

|      | Trig on HMASTER number.                                                                                                                                                                                                                                                        |      |

|      |                                                                                                                                                                                                                                                                                |      |

| 5120 | The trigger conditions of requirement 5110 are grouped in a register named 'Trigger Unit' (refer to section 6). The IPMON shall implement between 1 and 4 trigger units (configurable using a constant). The trigger unit registers shall be configurable through the APB bus. |      |

|      |                                                                                                                                                                                                                                                                                |      |

| 5130 | The trigger function shall generate 4 trigger events:                                                                                                                                                                                                                          |      |

|      | • Start Trace (ST)                                                                                                                                                                                                                                                             |      |

|      | • End of Trace (ET)                                                                                                                                                                                                                                                            |      |

|      | • Start Statistics (SS)                                                                                                                                                                                                                                                        |      |

|      | • End of Statistics (ES)                                                                                                                                                                                                                                                       |      |

|      |                                                                                                                                                                                                                                                                                | <br> |

| 5140 | It shall be possible that each of the 4 trigger events can be triggered by any combination of the trigger units. This shall be configurable through the Event Configuration registers (defined in section 6).                                                                  |      |

NbCars NbWords FileName

38578 7475 IPMON\_SPEC\_ARCHI\_103\_R00.doc

Ref : R&D.SCOC3.RP.00539.V.ASTR

Issue : 03 Rev. :00 Date : 2008/05/05

Page : 13

The Start Trace and Start Statistics events shall be generated conditionally (by Trigger Units) only when the 'Enable Conditional Start' fields of the Control Register are equal to 1. Once such a generation occurred, these fields shall be set to 0. Therefore, after they have stopped, trace or statistics functions shall not start again automatically if the same trigger condition occurs on the bus.

In case one of the internal registers used to compute trace and statistics data (Wait States, Grant Delay, or Split time counter) reaches its maximum value, the trace and the statistics functions shall stop and an interrupt (it\_error) shall be generated.

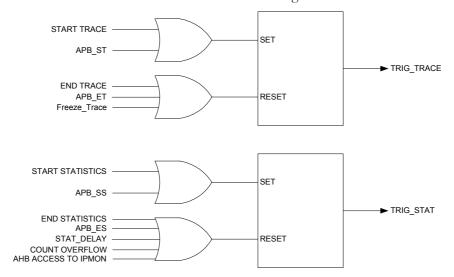

5150 Finally, the trace function shall start when:

ST event is activated and conditional start is enabled or Bit APB\_ST of the APB\_TRIG\_REG is activated

And shall stop when:

• ET event is activated **or** Bit APB\_ET of the APB\_TRIG\_REG is activated **or** the IPMON is accessed on its AHB slave interface **or** an Internal counter overflowed (it\_error) **or** Freeze\_trace pin is activated

5160 Finally, the statistics function shall start when:

SS event is activated and conditional start is enabled or Bit APB\_SS of the APB\_TRIG\_REG is activated

And shall stop when:

• ES event is activated **or** Bit APB\_ES of the APB\_TRIG\_REG is activated **or** the IPMON is accessed on its AHB slave interface **or** Statistics Delay Counter reached 0 **or** an Internal counter overflowed (it\_error) **or** one of the 10 registers composing the statistics word overflowed (cnt\_ovflow).

5170 The trigger function shall manage 2 status registers called:

- IPMON\_TRACE\_STATUS\_Reg

- IPMON\_STAT\_STATUS\_Reg

They shall contain, for each trigger event, the combination of the trigger units which were active when the event was triggered. A read of these registers shall

NbCars 3857

FileName IPMON\_SPEC\_ARCHI\_I03\_R00.doc

Ref : R&D.SCOC3.RP.00539.V.ASTR

Issue: 03 Rev. :00 Date : 2008/05/05

Page : 14

|      | clear their content when the trace/statistics function is not active (if the trace/statistics function is active, the TRACE_STATUS_REG/STAT_STATUS_REG shall not be cleared).                                                      |      |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|      |                                                                                                                                                                                                                                    |      |

| 5180 | When the trace/statistics functions are <b>started conditionally</b> , the access which triggered the activation shall <b>not be included</b> in the trace/statistics.                                                             |      |

|      | When the trace/statistics functions are <b>stopped conditionally</b> , the access which triggered the stop shall be <b>included</b> in the trace/statistics.                                                                       |      |

|      | When the trace/statistics functions are <b>stopped</b> by an access to the IPMON <b>AHB slave interface</b> , the access to the IPMON AHB slave interface shall <b>not be included</b> in the trace/statistics.                    |      |

|      | When the statistics function is <b>stopped</b> by a <b>cnt_ovflow interrupt,</b> the access which caused the counter overflow shall be <b>included</b> in the statistics (with at least one field saturated to its maximum value). | l    |

|      |                                                                                                                                                                                                                                    |      |

| 5190 | At the end of a hard reset (rstn input pin), the IPMON shall stay in a "soft reset" mode, to lower power consumption. To use the IPMON, the soft reset mode shall be left, by writing the IPM_RST field of the Control Register.   |      |

|      |                                                                                                                                                                                                                                    |      |

| 5.6  | INTERRUPT FUNCTION                                                                                                                                                                                                                 |      |

| 5200 | The IPMON shall include an interrupt function that manages 5 interrupt sources.                                                                                                                                                    |      |

|      |                                                                                                                                                                                                                                    |      |

| 5210 | In case of an interrupt, the corresponding bit of the IPMON Interrupt Status Register shall be raised as defined in section 6.                                                                                                     |      |

|      |                                                                                                                                                                                                                                    |      |

| 5220 | A read of the IPMON Interrupt Status Register shall clear the IPMON Interrupt Status Register.                                                                                                                                     |      |

|      |                                                                                                                                                                                                                                    | <br> |

| 5230 | The 5 interrupt bits of the IPMON Interrupt Status Register shall be ORed to generate the IT_IPMON signal, taking into account the mask defined in the IPMON Interrupt Mask Register.                                              |      |

NbCars NbWords FileName

38578 7475 IPMON\_SPEC\_ARCHI\_I03\_R00.doc

Ref : R&D.SCOC3.RP.00539.V.ASTR

Issue: 03 Rev. :00 Date : 2008/05/05

**Page** : 15

#### **REGISTERS DEFINITION** 6

| 6000 | The IPMON registers shall be programmable via the APB bus.                      |  |

|------|---------------------------------------------------------------------------------|--|

|      |                                                                                 |  |

| 6010 | The IPMON registers shall be compliant with the definitions given in section 6. |  |

NbCars NbWords FileName 38578 7475 IPMON\_SPEC\_ARCHI\_I03\_R00.doc

Ref : R&D.SCOC3.RP.00539.V.ASTR

Issue : 03 Rev. :00 Date : 2008/05/05

Page : 16

| Abbrev                     | Register name                                       | Address |

|----------------------------|-----------------------------------------------------|---------|

| IPMON_CTRL_Reg             | IPMON Control Register                              | 0x00    |

| IPMON_ST_CONF_Reg          | IPMON Start Trace Event Configuration Register      | 0x04    |

| IPMON_ET_CONF_Reg          | IPMON End Trace Event Configuration Register        | 0x08    |

| IPMON_SS_CONF_Reg          | IPMON Start Statistics Event Configuration Register | 0x0C    |

| IPMON_ES_CONF_Reg          | IPMON End Statistics Event Configuration Register   | 0x10    |

| IPMON_APB_TRIG_Reg         | IPMON APB Trig Register                             | 0x14    |

| IPMON_STAT_DELAY_Reg       | IPMON Statistics Delay Register                     | 0x18    |

| IPMON_IT_MASK_Reg          | IPMON Interrupt Mask Register                       | 0x1C    |

| IPMON_IT_STATUS_Reg        | IPMON Interrupt Status Register                     | 0x20    |

| IPMON_TRACE<br>_STATUS_Reg | IPMON Trace Status Register                         | 0x24    |

| IPMON_STAT<br>_STATUS_Reg  | IPMON Statistics Status Register                    | 0x28    |

| IPMON_GP1_TU1_Reg          | IPMON Global Purpose Register 1 associated with TU1 | 0x2C    |

| IPMON_GP2_TU1_Reg          | IPMON Global Purpose Register 2 associated with TU1 | 0x30    |

| IPMON_TU1_Reg              | IPMON Trigger Unit 1 Register                       | 0x34    |

| IPMON_GP1_TU2_Reg (*)      | IPMON Global Purpose Register 1 associated with TU2 | 0x38    |

| IPMON_GP2_TU2_Reg (*)      | IPMON Global Purpose Register 2 associated with TU2 | 0x3C    |

| IPMON_TU2_Reg (*)          | IPMON Trigger Unit 2 Register                       | 0x40    |

| IPMON_GP1_TU3_Reg (*)      | IPMON Global Purpose Register 1 associated with TU3 | 0x44    |

| IPMON_GP2_TU3_Reg (*)      | IPMON Global Purpose Register 2 associated with TU3 | 0x48    |

| IPMON_TU3_Reg (*)          | IPMON Trigger Unit 3 Register                       | 0x4C    |

| IPMON_GP1_TU4_Reg (*)      | IPMON Global Purpose Register 1 associated with TU4 | 0x50    |

| IPMON_GP2_TU4_Reg (*)      | IPMON Global Purpose Register 2 associated with TU4 | 0x54    |

| IPMON_TU4_Reg (*)          | IPMON Trigger Unit 4 Register                       | 0x58    |

Figure 4: List of the IPMON registers

(\*) if defined by the Nt constant. Reading a non defined register (i.e.: IPMON\_TU3\_Reg if only 2 trigger units are defined by the Nt constant) returns 0, and writing such a register does not have effect.

NbCars

38578

NbWords

7475

FileName

IPMON\_SPEC\_ARCHI\_103\_R00.doc

Ref : R&D.SCOC3.RP.00539.V.ASTR

Issue: 03 Rev. :00 Date : 2008/05/05

**Page** : 17

### Control Register (IPMON\_CTRL\_Reg): 0x00

| Bits | Field Name                                                                                                                                                                                                                                       | Description                                                                                                                                                                                                                                                                                         | r/w | Reset<br>Value |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------------|

| 314  | RESERVED                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                     |     | 0              |

| 3    | EN_COND_START_TR                                                                                                                                                                                                                                 | Enable Conditional Start Trace: The Start Trace event can be generated conditionally (by Trigger Units) only when this field is equal to 1. Once such a generation occurred, this field is set to 0. This field does not concern trace trig by APB.                                                 | r/w | 0              |

| 2    | Enable Conditional Start Stat: The Start Stat event can be generated conditionally (by Trigger Units) only when this field is equal to 1. Once such a generation occurred, this field is set to 0. This field does not concern stat trig by APB. |                                                                                                                                                                                                                                                                                                     | r/w | 0              |

| 1    | INIT_STAT_BUFFER                                                                                                                                                                                                                                 | Initialize Statistics Buffer: The statistics buffer is initialized when '1' is written in this field or at the end of a reset. While this field is equal to 1, the buffer is being initialized and: - trace/stat functions can't be activated - no access should occur on IPMON AHB slave interface | r/w | 0              |

| 0    | IPM_RST                                                                                                                                                                                                                                          | Soft Reset of the IPMON: resets all the registers. At the end of a hard reset, the IPMON is in Soft Reset mode (low power consumption mode). Write '0' in this field to quit the Soft Reset mode.                                                                                                   | r/w | 1              |

Figure 5: IPMON\_CTRL\_Reg register definition

NbCars NbWords FileName 7475 IPMON\_SPEC\_ARCHI\_I03\_R00.doc

Ref : R&D.SCOC3.RP.00539.V.ASTR

Issue: 03 Rev. :00 Date : 2008/05/05

Page : 18

### Event Configuration Registers (IPMON\_ST\_CONF\_Reg, IPMON\_ET\_CONF\_Reg, IPMON\_SS\_CONF\_Reg, IPMON\_ES\_CONF\_Reg): 0x04, 0x08, 0x0C, 0x10

| Bits | Field Name                                                        | Description                                                            | r/w | Reset<br>Value |

|------|-------------------------------------------------------------------|------------------------------------------------------------------------|-----|----------------|

| 3116 | RESERVED                                                          | Reserved                                                               | r   | 0              |

| 15   | TU4 & TU3 & TU2 &<br>TU1                                          | Trig event when the conditions of TU4 and TU3 and TU2 and TU1 are true | r/w | 0              |

| 14   | TU4 & TU3 & TU2                                                   | Trig event when the conditions of TU4 and TU3 and TU2 are true         | r/w | 0              |

| 13   | TU4 & TU3 & TU1                                                   | Trig event when the conditions of TU4 and TU3 and TU1 are true         | r/w | 0              |

| 12   | TU4 & TU3                                                         | Trig event when the conditions of TU4 and TU3 are true                 | r/w | 0              |

| 11   | TU4 & TU2 & TU1                                                   | Trig event when the conditions of TU4 and TU2 and TU1 are true         | r/w | 0              |

| 10   | TU4 & TU2                                                         | Trig event when the conditions of TU4 and TU2 are true                 | r/w | 0              |

| 9    | Tu4 & Tu1  Trig event when the conditions of Tu4 and Tu1 are true |                                                                        | r/w | 0              |

| 8    | TU4                                                               | TU4 Trig event when the conditions of TU4 are true                     |     | 0              |

| 7    | TU3 & TU2 & TU1                                                   | Trig event when the conditions of TU3 and TU2 and TU1 are true         | r/w | 0              |

| 6    | TU3 & TU2                                                         | Trig event when the conditions of TU3 and TU2 are true                 | r/w | 0              |

| 5    | TU3 & TU1                                                         | Trig event when the conditions of TU3 and TU1 are true                 | r/w | 0              |

| 4    | TU3                                                               | Trig event when the conditions of TU3 are true                         | r/w | 0              |

| 3    | TU1 & TU2                                                         | Trig event when the conditions of TU2 and TU1 are true                 | r/w | 0              |

| 2    | TU2                                                               | TU2 Trig event when the conditions of TU2 are true                     |     | 0              |

| 1    | TU1                                                               | Trig event when the conditions of TU1 are true                         | r/w | 0              |

| 0    | RESERVED                                                          | Reserved                                                               | r   | 0              |

Figure 6: IPMON\_XX\_CONF\_Reg register definition

When several conditions are set to 1, the event is triggered when any of them is true.

For example:

NbCars NbWords FileName 7475 IPMON\_SPEC\_ARCHI\_I03\_R00.doc

Ref : R&D.SCOC3.RP.00539.V.ASTR

Issue : 03 Rev. :00 Date : 2008/05/05

Page : 19

• Writing 1 in bit 6 of register IPMON\_ST\_Conf\_Reg allows the Start Trace event to be triggered when the conditions of Trigger Unit 2 and of Trigger Unit 3 are true.

• Writing 1 in bits 1 and 2 of register IPMON\_ST\_Conf\_Reg allows the Start Trace event to be triggered when the conditions of Trigger Unit 1 or of Trigger Unit 2 are true.

#### APB Trig register (IPMON\_APB\_TRIG\_Reg): 0x14

| Bits | Field Name | Description                         |     | Reset<br>Value |

|------|------------|-------------------------------------|-----|----------------|

| 314  | RESERVED   | Reserved                            | r   | 0              |

| 3    | APB_ES     | Trig End of Statistics by APB bus   | r/w | 0              |

| 2    | APB_SS     | Trig Start of Statistics by APB bus | r/w | 0              |

| 1    | APB_ET     | Trig End of Trace by APB bus        | r/w | 0              |

| 0    | APB_ST     | Trig Start of Trace by APB bus      | r/w | 0              |

Figure 7: IPMON\_APB\_TRIG\_Reg definition

The fields of the APB Trig register are automatically reset to 0 when the trig order has been taken into account.

#### Statistics Delay Register (IPMON\_STAT\_DELAY\_Reg): 0x18

| Bits | Field Name     | Description                                                            | r/w | Reset<br>Value |

|------|----------------|------------------------------------------------------------------------|-----|----------------|

| 310  | IPM_STAT_DELAY | Defines the maximum integration time (in clock cycles) for statistics. | r/w | 0              |

Figure 8: IPMON\_STAT\_DELAY\_Reg definition

NbCars

38578

NbWords

7475

FileName

IPMON\_SPEC\_ARCHI\_I03\_R00.doc

Ref : R&D.SCOC3.RP.00539.V.ASTR

Issue: 03 Rev. :00 Date : 2008/05/05

Page : 20

#### Interrupt Mask Register (IPMON\_IT\_MASK\_Reg): 0x1C

| Bits | Field Name                                                                         | Description                                                            | r/w | Reset<br>Value |

|------|------------------------------------------------------------------------------------|------------------------------------------------------------------------|-----|----------------|

| 315  | RESERVED                                                                           | Reserved                                                               | r   | 0              |

| 4    | IPM_IT_ MASK_ERROR When '0', mask IPM_IT_ERROR for the generation of the IT signal |                                                                        | r/w | 0              |

| 3    | IPM_IT_MSK_TRACE_FREEZE                                                            | When '0', mask IPM_IT_TRACE_FREEZE for the generation of the IT signal | r/w | 0              |

| 2    | IPM_IT_MSK_TRACE_STOP                                                              | When '0', mask IPM_IT_TRACE_STOP for the generation of the IT signal   | r/w | 0              |

| 1    | IPM_IT_MSK_STAT_CNT                                                                | When '0', mask IPM_IT_STAT_CNT for the generation of the IT signal     | r/w | 0              |

| 0    | IPM_IT_MSK_STAT_STOP                                                               | When '0', mask IPM_IT_STAT_STOP for the generation of the IT signal    | r/w | 0              |

Figure 9: IPMON\_IT\_MASK\_Reg definition

#### Interrupt Status Register (IPMON\_IT\_STATUS\_Reg): 0x20

| Bits | Field Name                                                                                                                                                                  | Tame Description                                                                                                                                                                |   | Reset |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-------|

|      |                                                                                                                                                                             |                                                                                                                                                                                 |   | Value |

| 315  | RESERVED                                                                                                                                                                    | Reserved                                                                                                                                                                        | r | 0     |

| 4    | IPM_IT_ERROR                                                                                                                                                                | Indicates that one of the internal registers (Wait States, Grant Delay, or Split time counter) has reached its maximum value, thus stopping both trace and statistics functions |   | 0     |

| 3    | IPM_IT_TRACE_FREEZE                                                                                                                                                         | Indicates that trace function has stopped because external Freeze_Trace pin was activated                                                                                       | r | 0     |

| 2    | IPM_IT_TRACE_STOP                                                                                                                                                           | Indicates that trace function has stopped                                                                                                                                       |   | 0     |

| 1    | IPM_IT_STAT_CNT  IPM_IT_STAT_CNT  Indicates that one of the 10 registers composing the statistics word has reached its maximum value, thus stopping the statistics function |                                                                                                                                                                                 | f | 0     |

| 0    | IPM_IT_STAT_STOP                                                                                                                                                            | Indicates that statistics function has stopped                                                                                                                                  | r | 0     |

Figure 10: IPMON\_IT\_STATUS\_Reg definition

The Interrupt Status Register is reset when it is read by APB.

NbCars NbWords FileName

7475 IPMON\_SPEC\_ARCHI\_I03\_R00.doc

Ref : R&D.SCOC3.RP.00539.V.ASTR

Issue: 03 Rev. :00 Date : 2008/05/05

Page : 21

#### Trace Status Register (IPMON\_TRACE\_STATUS\_Reg): 0x24

| Bits | Field Name                                                                                                                                                                                                                                                                                                                                                                                                                                 | Description                                                                                                                                                                                                                                                                | r/w | Reset<br>Value |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------------|

| 3119 | RESERVED                                                                                                                                                                                                                                                                                                                                                                                                                                   | Reserved                                                                                                                                                                                                                                                                   | r   | 0              |

| 198  | Number of 128-bit words written in the trace buffer.  Value between 0 and 2048:  - When 0: no trace words have been written in the buffer.  - When between 1 and 1024: from 1 to 1024 words have been written in the trace buffer.  - When between 1025 and 2048: strictly more than 1024 words have been written, and the trace buffer rolled over. This field minus 1024 indicates the number of words written since the last roll over. |                                                                                                                                                                                                                                                                            | r   | 0              |

| 74   | ET_STATUS                                                                                                                                                                                                                                                                                                                                                                                                                                  | Reports which Trigger Units were active when the Trace function stopped (Bit 4 for TU1, bit 5 for TU2, etc.). Note that this field represents the status of <b>all</b> the Trigger Units (not only the status of the Trigger Units which triggered the End Trace event).   | f   | 0              |

| 30   | ST_STATUS                                                                                                                                                                                                                                                                                                                                                                                                                                  | Reports which Trigger Units were active when the Trace function started (Bit 0 for TU1, Bit 1 for TU2, etc.). Note that this field represents the status of <b>all</b> the Trigger Units (not only the status of the Trigger Units which triggered the Start Trace event). | r   | 0              |

Figure 11: IPMON\_TRACE\_STATUS\_Reg definition

IPMON\_TRACE\_STATUS\_Reg fields are reset when they are read by APB while Trace function is stopped (if Trace function is active, they are not reset).

NbCars NbWords FileName 7475 IPMON\_SPEC\_ARCHI\_I03\_R00.doc

Ref : R&D.SCOC3.RP.00539.V.ASTR

Issue : 03 Rev. :00 Date : 2008/05/05

Page : 22

#### Statistics Status Register (IPMON\_STAT\_STATUS\_Reg): 0x28

| Bits | Field Name                                                                                                                                                                                                                                                                                        | Description                                                                                                                                                                                                                                                                        | r/w | Reset Value |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------|

| 31 8 | RESERVED                                                                                                                                                                                                                                                                                          | Reserved                                                                                                                                                                                                                                                                           |     | 0           |