Pag. 1 / 45

# IP Core for Medium Data Rate PDT

Final Report

ESA Contract 4000117901/16/NL/FE/eg

> Revision 1.0 Date 10/07/2018

| Preparato/Prepared        | Approvato/Approved      | Autorizzato/Authorized |

|---------------------------|-------------------------|------------------------|

| R. Cassettari, D. Davalle | S. Saponara, L. Fanucci | L. Fanucci             |

aiceanto lossathai seguilgorren (Cenela Maralle

Mee Farmeci

Doc. No: ING-IPCTM-FR-v1.0 - 10/07/2018

Pag. 2 / 45

# Change Record

| Rev |     | Date       | Change description | Edited         |

|-----|-----|------------|--------------------|----------------|

|     | 1.0 | 10/07/2018 | First issue        | R. Cassettari, |

|     |     |            |                    | D. Davalle     |

Pag. 3 / 45

## Contents

| 1 | Int | rodu  | uction                            | 6  |

|---|-----|-------|-----------------------------------|----|

|   | 1.1 | Sco   | ppe                               | 6  |

|   | 1.2 | Do    | cuments                           | 6  |

|   | 1.2 | 2.1   | Applicable documents              | 6  |

|   | 1.3 | Def   | finitions and Acronyms            | 6  |

|   | 1.3 | 3.1   | Definitions                       | 6  |

|   | 1.3 | 3.2   | Acronyms                          | 6  |

| 2 | Ov  | /ervi | ew                                | 8  |

| 3 | Ar  | chite | ecture Description                | 11 |

|   | 3.1 | ccs   | ds_tm_top                         | 11 |

|   | 3.1 | 1.1   | Data-path optimisation            | 16 |

|   | 3.1 | 1.2   | Buffering strategy and throughput | 23 |

|   | 3.1 | 1.3   | Generics                          | 25 |

|   | 3.1 | 1.4   | Ports                             | 28 |

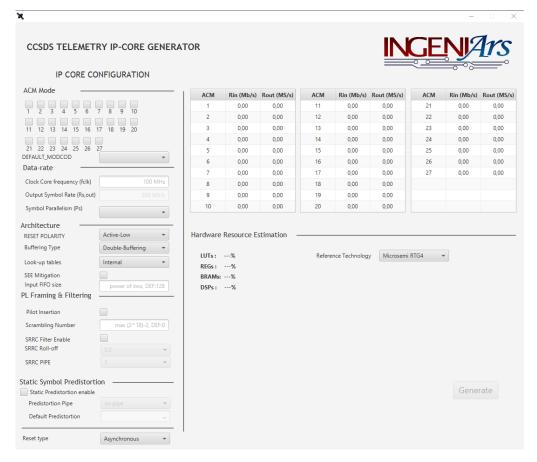

|   | 3.2 | Gra   | aphical User Interface            | 34 |

| 4 | Te  | chn   | ology mapping results             | 39 |

|   | 4.1 | BEI   | R Performance                     | 41 |

| 5 | Va  | ılida | tion set-up                       | 43 |

Pag. 4 / 45

# List of Figures

| Figure 2-1 IP Core High-level functional block diagram             | 8  |

|--------------------------------------------------------------------|----|

| Figure 3-1 Input FIFO data alignment                               |    |

| Figure 3-2 IP core architecture                                    | 15 |

| Figure 3-3 Data-rates within the SCCC encoder                      |    |

| Figure 3-4 Double buffering architecture timing diagram            | 23 |

| Figure 3-5 Single buffering architecture timing diagram            | 23 |

| Figure 3-6 CCSDS Telemetry Transmitter IP Core top-level interface | 28 |

| Figure 3-7 Input data interface timing                             | 29 |

| Figure 3-8 Output data interface timing                            | 31 |

| Figure 3-9 Configuration and status interface timing               | 32 |

| Figure 3-10 LUT loader interface timing                            | 33 |

| Figure 3-11 IP Core Graphical User Interface                       | 35 |

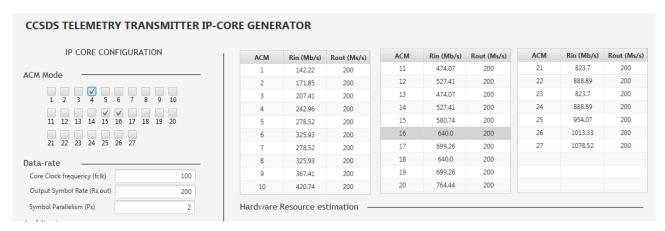

| Figure 3-12 Example of ModCods ad output symbol rate setting       | 36 |

| Figure 3-13 Architecture panel options                             | 36 |

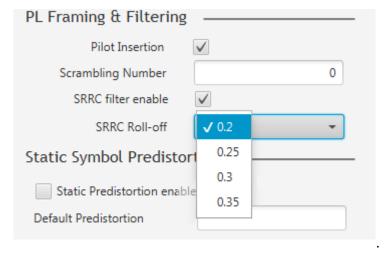

| Figure 3-14 PL Framing and Filtering setting example               | 36 |

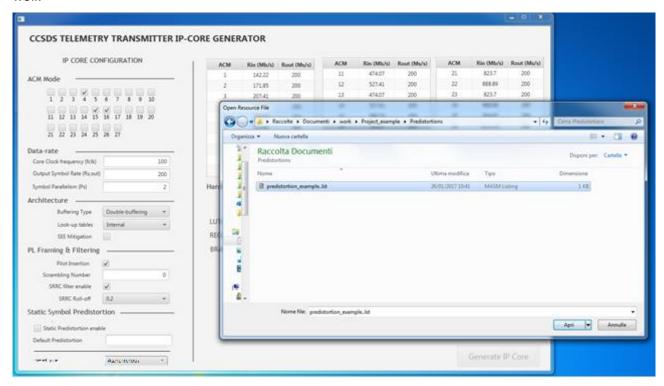

| Figure 3-15 Predistortion file selection example                   | 37 |

| Figure 3-16 Predistortion file format                              | 37 |

| Figure 3-17 Target technology selection                            | 38 |

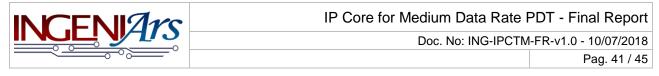

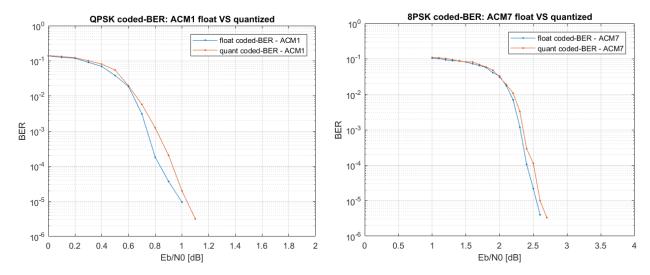

| Figure 4-1 IP core BER performance for ACM1 and ACM7               | 41 |

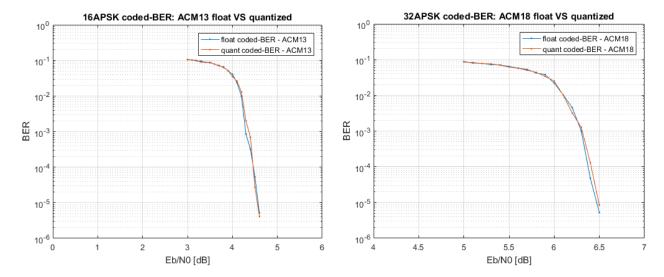

| Figure 4-2 IP core BER performance for ACM13 and ACM18             | 41 |

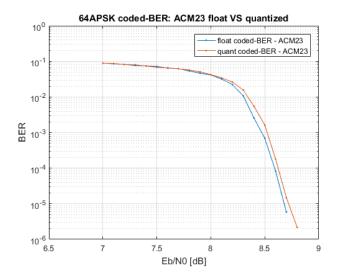

| Figure 4-3 IP core BER performance for ACM23                       | 42 |

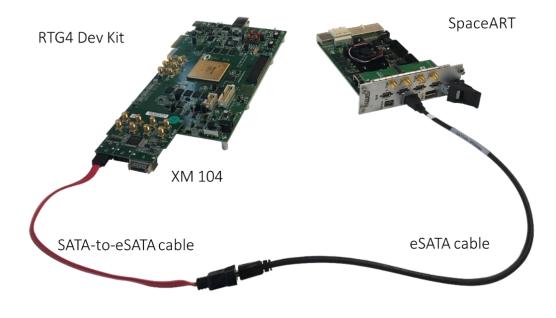

| • Figure 5-1 HW set-up                                             | 44 |

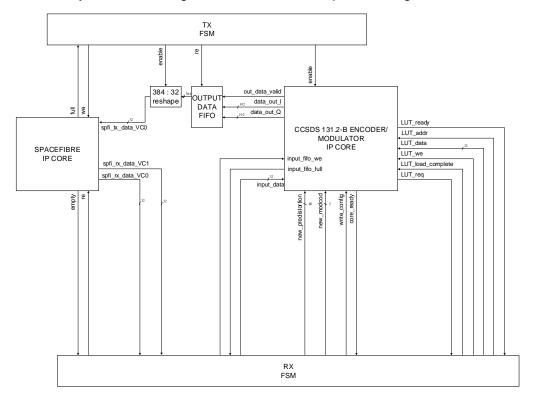

| Figure 5-2 Validation System, FPGA Block Diagram                   | 44 |

Doc. No: ING-IPCTM-FR-v1.0 - 10/07/2018

Pag. 5 / 45

# List of Tables

| Table 1-1 Definitions                                                                   | 6  |

|-----------------------------------------------------------------------------------------|----|

| Table 1-2 Acronyms                                                                      | 7  |

| Table 2-1 Encoder parameters for the 27 supported ModCods                               | 10 |

| Table 3-1 Theoretical and supported data rates into the SCCC encoder                    | 18 |

| Table 3-2 Architecture parallelism parameters for Ps = 1                                | 20 |

| Table 3-3 Architecture parallelism parameters for Ps = 2                                | 21 |

| Table 3-4 Architecture parallelism parameters for Ps = 4                                | 22 |

| Table 3-5 Top-level Generic Map                                                         | 27 |

| Table 3-6 Input data interface                                                          | 29 |

| Table 3-7 Output data interface                                                         | 30 |

| Table 3-8 Configuration and status interface                                            | 31 |

| Table 3-9 LUT loader interface                                                          | 33 |

| Table 3-10 Clock, reset and enable interface                                            | 34 |

| Table 4-1 ModCod support on the different technologies                                  | 39 |

| Table 4-2 Multiple-ModCod instantiation synthesis results on the different technologies | 40 |

| Table 4-3 IP core post place and route performance                                      | 41 |

# 1 Introduction

## 1.1 Scope

This document represents the Final Report for the activity "IP Core for Medium Data Rate PDT" initiated by the European Space Agency under ESTEC contract 400117901/16/NL/FE/eg

#### 1.2 Documents

## 1.2.1 Applicable documents

| AD     | Doc. No.         | Issue/<br>Rev. | Title                                                                               |

|--------|------------------|----------------|-------------------------------------------------------------------------------------|

| [AD01] | CCSDS 131.2-B-1  | 1              | Flexible advanced coding and modulation scheme for high rate telemetry applications |

| [AD02] | TEC-ETC/2015.172 | 2              | Statement of Work - IP Core for Medium Data Rate PDT                                |

## 1.3 Definitions and Acronyms

#### 1.3.1 Definitions

Recurring definitions are reported in the following table.

| Definition         | Description                                                                                                                                                                                                                                                                 |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Hard configuration | Configuration item selected during IP core generation or through code parameter, which cannot change at run-time. Hard configuration parameters are typically used to optimize the specific implementation of the IP core, while maintaining a more general purpose IP core |

| ModCod             | Modulation and Coding scheme                                                                                                                                                                                                                                                |

| Soft configuration | Configuration item which can be modified at run-time, e.g., through configuration registers.                                                                                                                                                                                |

Table 1-1 Definitions

## 1.3.2 Acronyms

Acronyms used in the present document are listed in the following table.

| Acronym Description |                                            |  |

|---------------------|--------------------------------------------|--|

| ACM                 | Adaptive Coding and Modulations            |  |

| CDC                 | Clock Domain Crossing                      |  |

| FFT                 | Fast Fourier Transform                     |  |

| FIFO                | First In First Out                         |  |

| FIR                 | Finite Impulse Response                    |  |

| GUI                 | Graphical User Interface                   |  |

| HPA                 | High Power Amplifier                       |  |

| LUT                 | Look-Up Table                              |  |

| PL                  | Physical Layer                             |  |

| SCCC                | Serially Concatenated Convolutional Coding |  |

# IP Core for Medium Data Rate PDT - Final Report Doc. No: ING-IPCTM-FR-v1.0 - 10/07/2018

Pag. 7 / 45

| Acronym | Description                         |

|---------|-------------------------------------|

| SEE     | Single Event Effect                 |

| SRRC    | Square Root Raised Cosine           |

| VHDL    | VHSIC Hardware Description Language |

Table 1-2 Acronyms

Pag. 8 / 45

## 2 Overview

The IP Core for Medium Data Rate PDT implements a Serially Concatenated Convolutional Coding (SCCC) scheme for telemetry application, which functionality is compliant with CCSDS 131.2-B-1 standard. The transmitter makes use of a large variety of modulation schemes (including QPSK, 8-PSK, 16-APSK, 32-APSK and 64-APSK) and a wide range of coding rates.

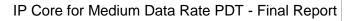

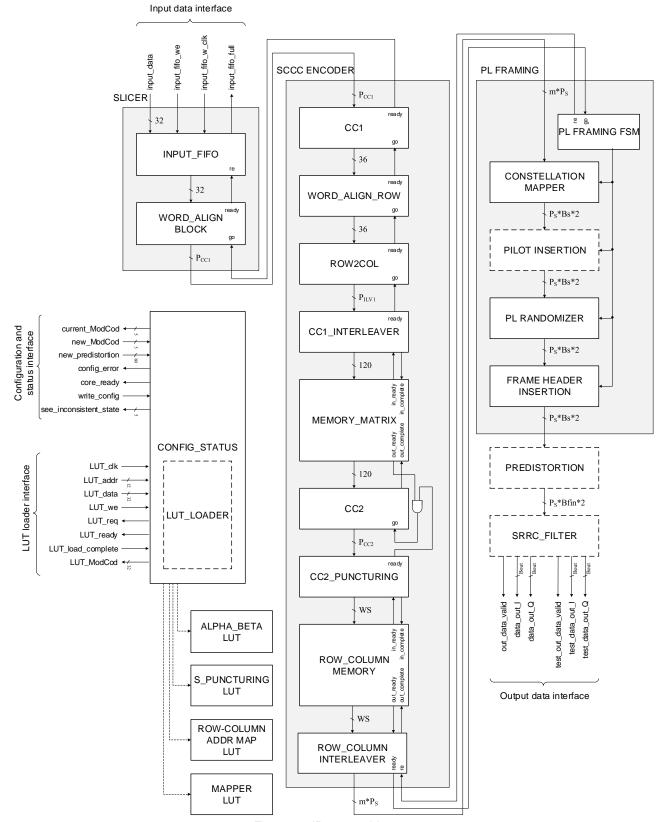

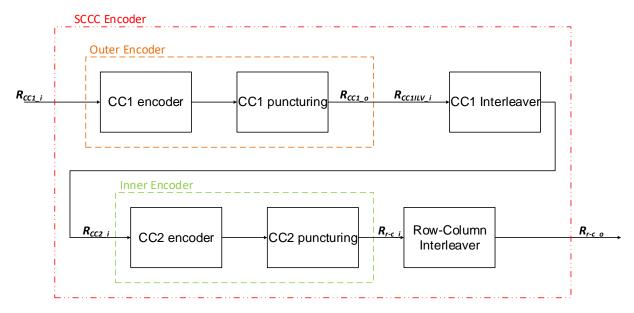

The high-level functional block diagram of the CCSDS telemetry transmitter IP core is presented in Figure 2-1.

Figure 2-1 IP Core High-level functional block diagram

The functionality of each block in the processing chain is described in the following. The algorithm consists of two main functional blocks: 1) a Serially Concatenated Convolutional Coding (SCCC) Encoder and 2) a Physical Layer (PL) framing block. Other functional blocks, which take place before the Slicer block in the processing chain, are defined in [AD01], but they are not implemented in this IP Core and then will not be described in this document. More details about these functional blocks and the algorithms used in the Telemetry Transmitter can be found in the CCSDS 131.2-B standard. Table 2-1 contains the algorithm parameters for the encoder processing, as defined in [AD01] and which are widely used in the rest of the document for the description of the architecture.

Pag. 9 / 45

In detail, the processing chain is composed by the following blocks:

- **Slicer:** this block has to split the input CADU stream into a sequence of information blocks of length *K*, corresponding to the information block size of the selected ModCod.

- Outer encoder (CC1): performs the first convolutional encoding and the output bit-stream is punctured by decimating the parity bits by half for an overall coding rate of 2/3. The input data block has length K bits and the output data block has length I bits.

- **CC1 interleaver**: this block implements the ad-hoc interleaving law described in the annex B of the CCSDS 131.2-B standard, which makes extensive use of Look-Up Tables. The input/output data block has length / bits.

- Inner Encoder (CC2): carries out the second convolutional encoding, with the same algorithm as the outer encoder. Puncturing adjusts the data size of the block in order to fit the 8100 output symbols. Differently from outer puncturing, the puncturing after inner encoder is much more complex as it is composed by different algorithms for puncturing systematic bits and parity bits. The input data block has length *I* bits, and the output data block is punctured to have 8100 output symbols for all the ModCods, therefore, the number of output bits for each ModCod is  $8100 \cdot m$ , where m is the modulation index relative to the ModCod.

- Row-Column Interleaver: is used to interleave the bits that are assigned to symbols. The input to the Row-Column interleaver are the systematic bits followed by the parity bits from the punctured output of the inner encoder.

- **Constellation Mapping**: is used to map the SCCC encoded bit-stream to symbols, according to the modulation index defined in each ModCod.

- PL Signalling Insertion: is used to frame the sequence of codewords sections, each composed of 8100 symbols. A frame header segment is added every 16 codeword sections (codeword segment). The frame header together with the codeword segment constitutes the Physical Layer Frame.

- **Pilot Insertion**: is used to include a pilot sequence to facilitate carrier and phase synchronization. The pilot insertion is an optional functional block and it is possible to bypass it at IP Core instantiation.

- **PL Pseudo-Randomiser**: is used to have a sufficient number of bit transitions in order to allow proper synchronisation of the decoder.

- **Symbol pre-distortion**: is used to correct HPA non-linearities, both in phase and amplitude, by multiplication with a constant complex pre-distortion coefficient on the output symbols, right before baseband filtering. The symbol pre-distortion is an optional functional block and it is possible to bypass it at IP Core instantiation.

- Baseband filtering: performs Square Root Raised Cosine (SRRC) pulse-shaping on I and Q arms, with the roll-off options given in the CCSDS 131.2-B standard. The baseband filtering is an optional functional block and it is possible to bypass it at IP Core instantiation.

Doc. No: ING-IPCTM-FR-v1.0 - 10/07/2018

Pag. 10 / 45

| ModCod | Information<br>block size<br>(bits) (K) | Information<br>W (Wi) | outer CC<br>output after<br>puncturing<br>(bits) (I) | Interleaver<br>W | Systematic<br>bits after<br>inner CC<br>puncturing<br>(S) | Parity bits<br>after inner<br>CC<br>puncturing<br>(P) | inner<br>CC<br>output<br>(bits) | Modula<br>tion<br>index<br>(m) |

|--------|-----------------------------------------|-----------------------|------------------------------------------------------|------------------|-----------------------------------------------------------|-------------------------------------------------------|---------------------------------|--------------------------------|

| 1      | 5758                                    | 48                    | 8640                                                 | 72               | 8642                                                      | 7558                                                  | 16200                           | 2                              |

| 2      | 6958                                    | 58                    | 10440                                                | 87               | 10442                                                     | 5758                                                  | 16200                           | 2                              |

| 3      | 8398                                    | 70                    | 12600                                                | 105              | 11510                                                     | 4690                                                  | 16200                           | 2                              |

| 4      | 9838                                    | 82                    | 14760                                                | 123              | 12351                                                     | 3849                                                  | 16200                           | 2                              |

| 5      | 11278                                   | 94                    | 16920                                                | 141              | 13200                                                     | 3000                                                  | 16200                           | 2                              |

| 6      | 13198                                   | 110                   | 19800                                                | 165              | 14390                                                     | 1810                                                  | 16200                           | 2                              |

| 7      | 11278                                   | 94                    | 16920                                                | 141              | 16470                                                     | 7830                                                  | 24300                           | 3                              |

| 8      | 13198                                   | 110                   | 19800                                                | 165              | 15842                                                     | 8458                                                  | 24300                           | 3                              |

| 9      | 14878                                   | 124                   | 22320                                                | 186              | 18602                                                     | 5698                                                  | 24300                           | 3                              |

| 10     | 17038                                   | 142                   | 25560                                                | 213              | 19939                                                     | 4361                                                  | 24300                           | 3                              |

| 11     | 19198                                   | 160                   | 28800                                                | 240              | 21218                                                     | 3082                                                  | 24300                           | 3                              |

| 12     | 21358                                   | 178                   | 32040                                                | 267              | 22857                                                     | 1443                                                  | 24300                           | 3                              |

| 13     | 19198                                   | 160                   | 28800                                                | 240              | 24482                                                     | 7918                                                  | 32400                           | 4                              |

| 14     | 21358                                   | 178                   | 32040                                                | 267              | 25741                                                     | 6659                                                  | 32400                           | 4                              |

| 15     | 23518                                   | 196                   | 35280                                                | 294              | 27051                                                     | 5349                                                  | 32400                           | 4                              |

| 16     | 25918                                   | 216                   | 38880                                                | 324              | 28515                                                     | 3885                                                  | 32400                           | 4                              |

| 17     | 28318                                   | 236                   | 42480                                                | 354              | 29880                                                     | 2520                                                  | 32400                           | 4                              |

| 18     | 25918                                   | 216                   | 38880                                                | 324              | 31755                                                     | 8745                                                  | 40500                           | 5                              |

| 19     | 28318                                   | 236                   | 42480                                                | 354              | 33137                                                     | 7363                                                  | 40500                           | 5                              |

| 20     | 30958                                   | 258                   | 46440                                                | 387              | 34677                                                     | 5823                                                  | 40500                           | 5                              |

| 21     | 33358                                   | 278                   | 50040                                                | 417              | 36197                                                     | 4303                                                  | 40500                           | 5                              |

| 22     | 35998                                   | 300                   | 54000                                                | 450              | 37802                                                     | 2698                                                  | 40500                           | 5                              |

| 23     | 33358                                   | 278                   | 50040                                                | 417              | 39366                                                     | 9234                                                  | 48600                           | 6                              |

| 24     | 35998                                   | 300                   | 54000                                                | 450              | 41042                                                     | 7558                                                  | 48600                           | 6                              |

| 25     | 38638                                   | 322                   | 57960                                                | 483              | 42507                                                     | 6093                                                  | 48600                           | 6                              |

| 26     | 41038                                   | 342                   | 61560                                                | 513              | 43915                                                     | 4685                                                  | 48600                           | 6                              |

| 27     | 43678                                   | 364                   | 65520                                                | 546              | 45429                                                     | 3171                                                  | 48600                           | 6                              |

|        |                                         |                       |                                                      |                  |                                                           |                                                       |                                 |                                |

Table 2-1 Encoder parameters for the 27 supported ModCods

## 3 Architecture Description

The following sections contain the description of the top-level architecture of the CCSDS Telemetry Transmitter IP-core.

## 3.1 ccsds\_tm\_top

This represents the top-level entity of CCSDS Telemetry transmitter IP core.

In general, a fully synchronous approach has been adopted, avoiding internal clock-domain crossings. In order to deal with host system integration, some interfaces are driven by a different clock with respect to the IP core clock, provided by the host. The resulting clock-domain crossings (CDC) are limited to those interfaces and are treated with well-known methods such as asynchronous FIFO, which totally eliminate the problems involved with CDC.

The global reset signal will be connected to all flip-flops without combinational logic. The reset behavior is configurable by hard configuration: active-high/active low; synchronous/asynchronous.

Figure 3-2 shows the IP-core architecture, which consists of the following blocks:

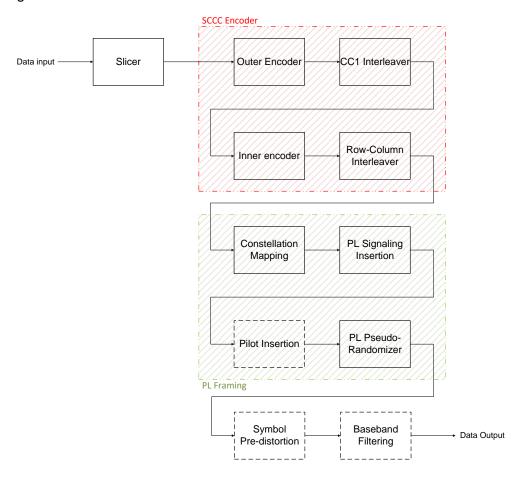

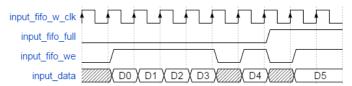

- The Slicer, which has the task of reorganizing the input data stream for the next processing. Figure 3-1 shows how the blocks of data are written and organised into the input FIFO. In general the block size K (variable with the ModCod selected) is not a multiple of the FIFO word length, L = 32, therefore it is necessary to realign the data for the subsequent processing. The asynchronous FIFO is used by the external host to write data to the IP-core for processing. The FIFO is read internally by the word align block which organises data for the outer convolutional encoder (CC1 encoder). The slicer is composed by:

- input\_fifo: the input FIFO buffer represents the external host interface of the IP Core and provides a simple FIFO interface composed of a 32-bit input data bus, the writeenable and the fifo-full flag. Writing into FIFO is managed using an external clock domain, which is given as input to the IP Core. The input FIFO is asynchronous to allow easy integration in the IP core host system.

- $\circ$  **word\_align\_block**: this block is used to extract the  $P_{cc1}$  bits word which shall be processed in parallel by the outer convolutional encoder, keeping alignment to the input data block of  $P_{cc1}$  is a generic parameter of the IP Core.

- The SCCC encoder, which performs in cascade:

- o **CC1**, the outer convolutional encoder, features an innovative data processing architecture, which allows to optimize resource optimization.

- word\_align\_row this block and the following row2col block have the task of reshaping the data to be provided to the CC1 Interleaver block, the CC1 Interleaver works on data organised as a matrix of 120 rows and W columns, where W is a specific parameter of the transmitter defined in [AD01] and depends on the ModCod

Pag. 12 / 45

Figure 3-1 Input FIFO data alignment

selected (see Table 2-1). The word align block in particular provides 36-bit data words aligned to the row's length W, i.e., after alignment, each row starts on the lsb of the 36-bit output word and each 36-bit word will contain data belonging to one row only. This aspect is fundamental as in the following processing contiguous rows shall be accessed simultaneously and each row is stored in a different memory block to achieve this.

- o **row2col**, this block transposes data of the input data matrix, which is then read column by column by the CC1 interleaver,  $P_{ILV}$  bits per clock cycle.  $P_{ILV}$  is a generic parameter of the IP Core.

- o **cc1\_interleaver**, this block implements the interleaver law described in [AD01]. The input data matrix is read column by column to implement the algorithm efficiently. The input data matrix is segmented, i.e., instead of processing whole columns,  $P_{ILV}$ -bit column segments are processed, in order to reduce the complexity. The output is stored in a memory matrix, implemented with RAM blocks. The CC1 interleaver processes  $P_{ILV}$  bits per clock cycle.  $P_{ILV}$  is in general less than 120 (column length),

Pag. 13 / 45

thus, a column in the memory matrix is partially written  $120/P_{ILV}$  times during the interleaving processing.

- memory\_matrix, this block stores the output data of the Interleaver processing in a RAM of W words of size 120. The maximum W depends on the ModCods supported in a certain instantiation of the IP core (see Table 2-1 for the correspondence between W and ModCod). Data for the following processing block is valid only after the completion of the Interleaver processing thus, in order to avoid interruptions in the data path processing, two memory matrices working in ping-pong are expected at this stage, i.e., while the Interleaver is writing in one memory, the Inner Encoder can read and process data from the second memory and vice-versa. The IP Core generic BUFFERING\_TYPE allows an implementation of the memory matrix either as ping-pong memory, or as a single memory to reduce hardware complexity at the price of a lower data rate achievable.

- occ2, this block implements the same encoding algorithm used in the Outer Encoder, however with a different architecture. Where the outer encoder processes data rowwise, the inner encoder processes data column-wise, to have an efficient integration with the CC1 interleaver. In order to reduce hardware complexity, CC2 is able to elaborate column segments other than full columns, i.e.,  $P_{cc2}$  rows of the memory matrix at a time. The elaboration of each  $P_{cc2}$  rows segment requires two passes, which means  $2 \cdot W$  clock cycles. In the first pass, the  $P_{cc2}$  rows of the memory matrix are read to calculate the initial states for each sub-trellis. During the first pass, the output of CC2 are the systematic bits. During the second pass, the  $P_{cc2}$  rows are read again to produce the related parity bits. The encoding of the whole data matrix lasts  $2 \cdot W \cdot \frac{120}{P_{CC2}}$  clock cycles, where  $P_{cc2}$  is a generic parameter of the IP Core.

- cc2\_puncturing, this block performs the puncturing of both the systematic and parity bits produced by the Inner Encoder. In particular, the systematic bits are punctured during CC2 first pass, while the parity bits and punctured during CC2 second pass of each segment. Systematic and parity bits are punctured with different algorithms, as described in [AD01]. As for the Inner Encoder, this block processes P<sub>cc2</sub> bits in parallel. Output data is stored into the Row-Column memory.

- o row\_column\_memory. This memory consists of m RAM blocks of 8100 bits each, to facilitate the next row-column interleaver processing. Each RAM block corresponds to a column of the row-column interleaver. The Row-Column Interleaver cannot start the processing of the Row-Column memory until the Inner Puncturing block has terminated its processing. For this reason, in order to guarantee the continuous transmission of symbols, two memory buffers must be implemented in ping-pong.

- o **row-column interleaver**, this block reads *m* columns of the Row-Column memory in parallel, where *m* is the modulation index and depends on the selected ModCod. Each set of *m* bits represents a *symbol*. The Row-Column interleaver outputs *P*<sub>S</sub> symbols in parallel. The Row-Column interleaver produces 8100 symbols every input block of K bits. Data produced by the row-column interleaver constitutes the input for Physical Layer (PL) framing.

Pag. 14 / 45

• The **PL framing**, which performs the constellation mapping, the optional pilot insertion, symbol pseudo-randomization.

- o **frame\_header\_insertion**, this block generates the Frame Marker and Frame Descriptor fields to be inserted at the beginning of each PL frame. The architecture is able to produce  $P_S$  symbols per clock cycle. The modulation scheme used for these symbols is a  $\pi/2 BPSK$ .

- o **constellation\_mapper**, which translates the data symbols coming from the row-column interleaver in constellation symbols, depending on the modulation set. 10 different constellation maps are supported. The architecture is able to produce  $P_S$  symbols per clock cycle.

- o **pilot\_insertion**, this block inserts 16 Pilot symbols every 540 data symbols for a total of 240 Pilot symbols per Codeword section  $(240 \cdot 16 = 3840 \text{ pilot symbols in a whole PL frame})$ . The pilot insertion can be excluded in a given IP Core instantiation through the generic parameter PILOT\_INSERTION.

- o **pl\_randomizer**, which generates the pseudo-random sequence used to randomize the data and pilots symbols. The frame Header symbols are not randomized. The pseudo-random sequence is reset at the end of each PL frame. The architecture of this block is able to randomize  $P_S$  symbols per clock cycle.

- predistortion, this block is not specified in [AD01], symbol pre-distortion is provided in the IP Core to allow a first compensation of the amplitude/phase distortion introduced by the HPA. It implements a complex multiplication between the data symbols (as well as the pilot symbols when expected) and a specific set of pre-distortion parameters. It is possible to implement the pre-distortion parameters internally to the IP Core (as a LUT), or load them through the Configuration & status interface. In the first case, pre-distortion parameters can be set by the user through dedicated generics (see Table 3-5). The PREDISTORTION\_TYPE generic allows to select the desired pre-distortion parameters implementation.

- srrc\_filter, baseband SRRC filtering on both I and Q branches. The filter order is 47, supporting roll-off factor of 0.20, 0.25, 0.30, 0.35.  $P_S$  filtered symbols are provided in parallel, where  $P_S$  is a generic parameter of the IP Core, and each filtered symbols is represented in its real and imaginary part with 4 samples (4 is the designed samples per symbol, SRRC\_OVERSAMPLING). Output samples are provided in parallel  $4P_S$  per clock cycle, sample serialisation is up to the IP core user. The SRRC filter can be excluded in a given IP Core instantiation through the generic parameter SRRC\_ENABLE. In this case, the IP Core output will coincide with the output of the pre-distortion block.

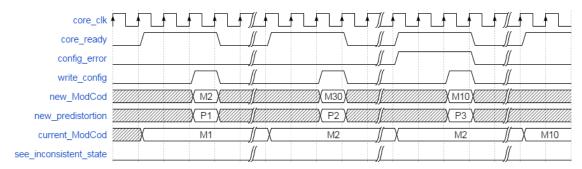

- config\_status, responsible of managing the IP core soft configuration process, providing the IP core status to the host system and loading the algorithm LUTs in case they are loaded externally.

Pag. 15 / 45

Figure 3-2 IP core architecture

The architecture was conceived with flexibility in mind. In order to easily adapt the IP core to many different use cases, it is provided with a complete set of hard configuration parameters, which allow enabling/disabling features of the processing, as well as optimizing the architecture in terms of

Block RAM data buses were set to 36 bits wherever convenient. This is seen as an optimal number in terms of memory management, as every reference target technology has a block RAM cut with word size 36 and the complexity given by this data-path size is acceptable.

performance/complexity trade-off. The hard configuration parameters are all accessible via the top-

The data flow was designed to have continuous transmission of symbols at the output, provided that continuous data is provided at the IP core input, i.e., the IP core input buffer never gets empty. To this aim, the producer blocks in the chain are designed to be faster than the final consumer block so that the output symbol buffer never gets empty, by design. However, due to this design choice, the buffers in the chain will unavoidably get full, therefore the producer blocks need to support processing stop-and-go. Each block in the processing chain is then provided with a ready output signal, indicating that the specific block is ready to take data for processing, and a go signal, enabling the processing of the specific block.

At the interleaver buffers, i.e., the memory\_matrix for CC1 interleaver and row-column memory for the row-column interleaver, the data flow control is managed with additional signals to efficiently handle both single and double buffering architectures. The data flow is regulated by the signals in\_ready, in\_complete, out\_ready, out\_complete. When the input write operation is complete, the producer asserts in\_complete, so that the buffer asserts out\_ready to inform the consumer that a data block is fully stored in the memory. In case single buffering is selected, in\_ready is deasserted by the buffer, so that the producer knows that it cannot write data to the buffer. When the consumer has read all the data block, it asserts out\_complete, so that the buffer is informed that a memory block can be freed, and the producer is informed through the assertion of in\_ready. When double-buffering is used, the buffer manages two memory blocks as a ping-pong memory, so that both the input and output interfaces are always ready, provided that the producer and the consumer operate steadily.

#### 3.1.1 Data-path optimisation

level generics and are described in Table 3-5.

This section describes all the architectural (i.e., parallelism) parameters which are managed by the IP Core generator and not visible to the final user. Once the "user-level" parameters are set through the GUI, all the linked parallelisation parameters are derived automatically by the software engine.

As a matter of fact, parallelisation parameters at each stage of the architecture might seem independent values at first sight, but in reality they are all linked to the output symbol rate. The optimum choice is the minimum parallelism that satisfies the required throughput at each stage. Therefore, once the output symbol rate is set, a certain data-rate is imposed to all the other stages of the processing; consequently all the other parameters are automatically extracted in order to sustain such a data-rate. In this way we obtain "classes" of optimised architecture parallelism and not all the possible combinations of the parallelisation parameters, which might be very inefficient.

Doc. No: ING-IPCTM-FR-v1.0 - 10/07/2018

Pag. 17 / 45

The main architecture parallelisation parameters, i.e., how many bits are processed per clock cycle, are four:

- 1.  $P_{CC1}$  which represents the parallelism at CC1.  $P_{CC1}$  must be a number such that  $P_{CC1} \cdot \frac{3}{2}$  is submultiple of 36 in order to simplify puncturing and reshaping for the subsequent memory write. Therefore it holds  $P_{CC1} \in \{2,4,6,8,12,24\}$

- 2.  $P_{ILV}$ , i.e. the parallelism at CC1 interleaver.  $P_{ILV}$  must be submultiple of 120 in order to effectively achieve the read-modify-write operation at CC1 interleaver. Therefore it holds  $P_{ILV} \in \{1, 2, 3, 4, 5, 6, 8, 10, 12, 15, 20, 24, 30, 40, 60, 120\}$

- 3.  $P_{CC2}$  is the parallelism at CC2.  $P_{CC2}$  must be as well submultiple of 120. Therefore it holds  $P_{CC2} \in \{1, 2, 3, 4, 5, 6, 8, 10, 12, 15, 20, 24, 30, 40, 60, 120\}$

- 4.  $P_S$  represents how many symbols are produced in parallel by the IP Core.  $P_S$ , together with the clock frequency defines the output symbol rate.  $P_S$  must be a power of two in order to reduce the complexity of the interface between the Row-Column interleaver and the Constellation mapper. Moreover too high values will result in a not-feasible implementation, since the corresponding Symbol data rate could not be sustained by the maximum input bitrate which is fixed by the 32-bit input bus. Therefore  $P_S \in \{1, 2, 4\}$

The parallelism parameters for the rest of the architecture are derived from these.

As mentioned, once the symbol rate parameter is set, a data-rate constraint is imposed to all the other stages. In this way all the other architecture parallelism parameters will be selected as the minimum value fulfilling the data-rate requirement for each stage (see Figure 3-3). In order to guarantee a continuous transmission of data, the "producer" blocks must always be faster than the "consumer" blocks in the processing chain, in this way the buffers will never get empty by design. Therefore, the processing chain will be designed to allow the interruption of processing as buffers will unavoidably get full.

Pag. 18 / 45

Figure 3-3 Data-rates within the SCCC encoder

The minimum required and the implemented bit-rates (the latter depending on the  $P_{CC1}$ ,  $P_{ILV}$  and  $P_{CC2}$  parameters previously described) at the various stages of the SCCC encoder can be computed with the equations in Table 3-1.

| MINIMUM REQUIRED data rate                                    | IMPLEMENTED data rate                                 |

|---------------------------------------------------------------|-------------------------------------------------------|

| $R_{sout}$                                                    | $R_{sout} = f_{clk} \cdot P_S (MS/s)$                 |

| $R_{r-c_o} = f_{clk} \cdot P_S \cdot m = R_{r-c_i} (Mb/s)$    | $R_{r-c\_o} = f_{clk} \cdot P_S \cdot m \ (Mb/s)$     |

| $R_{CC2\_i} = R_{r-c\_i} \cdot \frac{I}{8100 \cdot m} (Mb/s)$ | $R_{CC2\_i} = \frac{P_{CC2} \cdot f_{clk}}{2} (Mb/s)$ |

| $R_{CC1ILV\_i} = R_{CC2\_i}(Mb/s)$                            | $R_{CC1ILV\_i} = P_{ILV1} \cdot f_{clk}(Mb/s)$        |

| $R_{CC1\_o} = R_{CC1ILV\_i}(Mb/s)$                            | $R_{CC1\_o} = R_{CC1\_i} \cdot \frac{3}{2} (Mb/s)$    |

| $R_{CC1\_i} = R_{CC1\_o} \cdot \frac{2}{3} (Mb/s)$            | $R_{CC1\_i} = P_{CC1} \cdot f_{clk}(Mb/s)$            |

| T 11 0 TT 11 11 1                                             |                                                       |

Table 3-1 Theoretical and supported data rates into the SCCC encoder

$P_{\text{CC1}}$ ,  $P_{\text{ILV1}}$  and  $P_{\text{CC2}}$  parameters must be set in order to get the implemented data rates equal or greater than the theoretical ones. With this constraint we can re-elaborate the equations in Table 3-1 to get the following relationships between the  $P_{\text{S}}$  parameter and  $P_{\text{CC1}}$ ,  $P_{\text{ILV}}$  and  $P_{\text{CC2}}$  parameters:

$$P_{CC2} \ge 2 \cdot P_S \cdot \frac{I}{8100}$$

$$P_{ILV1} \ge P_S \cdot \frac{I}{8100}$$

Doc. No: ING-IPCTM-FR-v1.0 - 10/07/2018

Pag. 19 / 45

$$P_{CC1} \ge \frac{2}{3} \cdot P_S \cdot \frac{I}{8100}$$

The parameters must be then set considering that:

$$P_{S} \in \{1,2,4\}$$

$$P_{CC1} \in \{2,4,6,8,12,24\}$$

$$P_{ILV1} \in \{1,2,3,4,5,6,8,10,12,15,20,24,30,40,60,120\}$$

$$P_{CC2} \in \{1,2,3,4,5,6,8,10,12,15,20,24,30,40,60,120\}$$

Table 3-2, Table 3-3 and Table 3-4 show the selected  $P_{CC1}$ ,  $P_{ILV}$ ,  $P_{CC2}$  values for each ModCod, and the input/output data rates considering a reference clock frequency of 100 MHz, for  $P_s=1,2,4$ , respectively.

Pag. 20 / 45

| ModCod | P <sub>CC1</sub> | P <sub>ILV</sub> | P <sub>CC2</sub> | R <sub>b,in</sub><br>Mb/s | R <sub>s,out</sub><br>Ms/s |

|--------|------------------|------------------|------------------|---------------------------|----------------------------|

| 1      | 2                | 2                | 3                | 71.11                     | 100.00                     |

| 2      | 2                | 2                | 3                | 85.93                     | 100.00                     |

| 3      | 2                | 2                | 4                | 103.70                    | 100.00                     |

| 4      | 2                | 2                | 4                | 121.48                    | 100.00                     |

| 5      | 2                | 3                | 5                | 139.26                    | 100.00                     |

| 6      | 2                | 3                | 5                | 162.96                    | 100.00                     |

| 7      | 2                | 3                | 5                | 139.26                    | 100.00                     |

| 8      | 2                | 3                | 5                | 162.96                    | 100.00                     |

| 9      | 2                | 3                | 6                | 183.70                    | 100.00                     |

| 10     | 4                | 4                | 8                | 210.37                    | 100.00                     |

| 11     | 4                | 4                | 8                | 237.04                    | 100.00                     |

| 12     | 4                | 4                | 8                | 263.70                    | 100.00                     |

| 13     | 4                | 4                | 8                | 237.04                    | 100.00                     |

| 14     | 4                | 4                | 8                | 263.70                    | 100.00                     |

| 15     | 4                | 5                | 10               | 290.37                    | 100.00                     |

| 16     | 4                | 5                | 10               | 320.00                    | 100.00                     |

| 17     | 4                | 6                | 12               | 349.63                    | 100.00                     |

| 18     | 4                | 5                | 10               | 320.00                    | 100.00                     |

| 19     | 4                | 6                | 12               | 349.63                    | 100.00                     |

| 20     | 4                | 6                | 12               | 382.22                    | 100.00                     |

| 21     | 6                | 8                | 15               | 411.85                    | 100.00                     |

| 22     | 6                | 8                | 15               | 444.44                    | 100.00                     |

| 23     | 6                | 8                | 15               | 411.85                    | 100.00                     |

| 24     | 6                | 8                | 15               | 444.44                    | 100.00                     |

| 25     | 6                | 8                | 15               | 477.04                    | 100.00                     |

| 26     | 6                | 8                | 20               | 506.67                    | 100.00                     |

| 27     | 6                | 10               | 20               | 539.26                    | 100.00                     |

Table 3-2 Architecture parallelism parameters for Ps = 1

Pag. 21 / 45

| ModCod | P <sub>CC1</sub> | P <sub>ILV</sub> | P <sub>CC2</sub> | R <sub>b,in</sub><br>Mb/s | R <sub>s,out</sub><br>Ms/s |

|--------|------------------|------------------|------------------|---------------------------|----------------------------|

| 1      | 2                | 3                | 5                | 142.22                    | 200.00                     |

| 2      | 2                | 3                | 6                | 171.85                    | 200.00                     |

| 3      | 4                | 4                | 8                | 207.41                    | 200.00                     |

| 4      | 4                | 4                | 8                | 242.96                    | 200.00                     |

| 5      | 4                | 5                | 10               | 278.52                    | 200.00                     |

| 6      | 4                | 5                | 10               | 325.93                    | 200.00                     |

| 7      | 4                | 5                | 10               | 278.52                    | 200.00                     |

| 8      | 4                | 5                | 10               | 325.93                    | 200.00                     |

| 9      | 4                | 6                | 12               | 367.41                    | 200.00                     |

| 10     | 6                | 8                | 15               | 420.74                    | 200.00                     |

| 11     | 6                | 8                | 15               | 474.07                    | 200.00                     |

| 12     | 6                | 8                | 20               | 527.41                    | 200.00                     |

| 13     | 6                | 8                | 15               | 474.07                    | 200.00                     |

| 14     | 6                | 8                | 20               | 527.41                    | 200.00                     |

| 15     | 6                | 10               | 20               | 580.74                    | 200.00                     |

| 16     | 8                | 10               | 20               | 640.00                    | 200.00                     |

| 17     | 8                | 12               | 24               | 699.26                    | 200.00                     |

| 18     | 8                | 10               | 20               | 640.00                    | 200.00                     |

| 19     | 8                | 12               | 24               | 699.26                    | 200.00                     |

| 20     | 8                | 12               | 24               | 764.44                    | 200.00                     |

| 21     | 12               | 15               | 30               | 823.70                    | 200.00                     |

| 22     | 12               | 15               | 30               | 888.89                    | 200.00                     |

| 23     | 12               | 15               | 30               | 823.70                    | 200.00                     |

| 24     | 12               | 15               | 30               | 888.89                    | 200.00                     |

| 25     | 12               | 15               | 30               | 954.07                    | 200.00                     |

| 26     | 12               | 20               | 40               | 1013.33                   | 200.00                     |

| 27     | 12               | 20               | 40               | 1078.52                   | 200.00                     |

Table 3-3 Architecture parallelism parameters for Ps = 2

Pag. 22 / 45

| ModCod | P <sub>CC1</sub> | P <sub>ILV</sub> | P <sub>CC2</sub> | R <sub>b,in</sub><br>Mb/s | R <sub>s,out</sub><br>Ms/s |

|--------|------------------|------------------|------------------|---------------------------|----------------------------|

| 1      | 4                | 5                | 10               | 284.44                    | 400.00                     |

| 2      | 4                | 6                | 12               | 343.70                    | 400.00                     |

| 3      | 6                | 8                | 15               | 414.81                    | 400.00                     |

| 4      | 6                | 8                | 15               | 485.93                    | 400.00                     |

| 5      | 6                | 10               | 20               | 557.04                    | 400.00                     |

| 6      | 8                | 10               | 24               | 651.85                    | 400.00                     |

| 7      | 6                | 10               | 20               | 557.04                    | 400.00                     |

| 8      | 8                | 10               | 20               | 651.85                    | 400.00                     |

| 9      | 8                | 12               | 24               | 734.81                    | 400.00                     |

| 10     | 12               | 15               | 30               | 841.48                    | 400.00                     |

| 11     | 12               | 15               | 30               | 948.15                    | 400.00                     |

| 12     | 12               | 20               | 40               | 1054.81                   | 400.00                     |

| 13     | 12               | 15               | 30               | 948.15                    | 400.00                     |

| 14     | 12               | 20               | 40               | 1054.81                   | 400.00                     |

| 15     | 12               | 20               | 40               | 1161.48                   | 400.00                     |

| 16     | 24               | 20               | 40               | 1280.00                   | 400.00                     |

| 17     | 24               | 24               | 60               | 1398.52                   | 400.00                     |

| 18     | 24               | 20               | 40               | 1280.00                   | 400.00                     |

| 19     | 24               | 24               | 60               | 1398.52                   | 400.00                     |

| 20     | 24               | 24               | 60               | 1528.89                   | 400.00                     |

| 21     | 24               | 30               | 60               | 1647.41                   | 400.00                     |

| 22     | 24               | 30               | 60               | 1777.78                   | 400.00                     |

| 23     | 24               | 30               | 60               | 1647.41                   | 400.00                     |

| 24     | 24               | 30               | 60               | 1777.78                   | 400.00                     |

| 25     | 24               | 30               | 120              | 1908.15                   | 400.00                     |

| 26     | 24               | 40               | 120              | 2026.67                   | 400.00                     |

| 27     | 24               | 40               | 120              | 2157.04                   | 400.00                     |

Table 3-4 Architecture parallelism parameters for Ps = 4

## 3.1.2 Buffering strategy and throughput

In order to optimize the performance/complexity trade-off, the IP core allows the selection of the buffering strategy at CC1 interleaver, which can be either double buffering or single buffering.

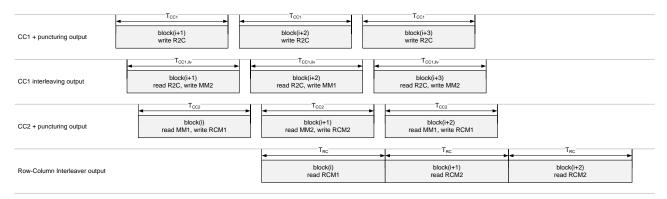

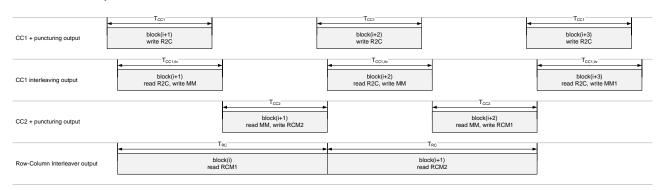

Figure 3-4 shows the timing diagram for the double buffering architecture. With the relations found among the parallelisation parameters in Section 3.1.1, the output of the row-column interleaver is continuous and therefore there is no risk of row-column buffer underrun, provided that the IP core input buffer never gets empty. This ensures that there will be no holes in the transmission as the symbol buffer is never empty by design.

Figure 3-4 Double buffering architecture timing diagram

Figure 3-5 shows the timing diagram for the single buffering architecture. In this scenario, the memory matrix contains only one data block, and does not work as a ping-pong memory. However, the row-column memory is forced to be double, otherwise it is not possible to achieve a continuous communication. In fact, considering that an entire block must be written to the row-column memory before being read by the row-column interleaver, it is not possible to read two blocks consecutively without interruption.

Figure 3-5 Single buffering architecture timing diagram

In order to guarantee the continuous transmission in case of single buffering architecture, the following condition must hold:

$$T_{RC} \geq T_{CC1.ilv} + T_{CC2}$$

Doc. No: ING-IPCTM-FR-v1.0 - 10/07/2018

Pag. 24 / 45

Where  $T_{RC}$  is the time required to produce the row-column interleaver output,  $T_{CC2}$  is the time required to produce the CC2 output  $T_{CC1,ilv}$  is the time required to produce the interleaver output. The relation ensures that when the row-column interleaver has finished processing a block, it has the next block available for processing in the row-column memory.

Given that:

$$T_{RC} = \frac{8100}{R_{S,out}}$$

,  $T_{CC1,ilv} = \frac{I}{R_{CC1,ilv,o}} = \frac{I}{P_{ILV}\,f_{ck}}$  and  $T_{CC2} = \frac{I}{R_{CC2,i}} = \frac{2I}{P_{CC2}\,f_{ck}}$ , it follows that

$$R_{S,out} \leq \frac{8100}{I} \frac{P_{ILV}P_{CC2}}{2P_{ILV} + P_{CC2}} f_{ck}$$

Which represents a limit on the output symbol rate, in order to slow down the reading of the row-column memory. With the values set for  $P_{ILV}$  and  $P_{CC2}$  in Table 3-2, Table 3-3 and Table 3-4, it holds:

$$\frac{8100}{I} \frac{P_{ILV} P_{CC2}}{2 P_{ILV} + P_{CC2}} \ge \frac{P_S}{2}$$

Then, the output symbol rate with the single buffering architecture can be set to  $R_{s,out,sb} = \frac{P_s f_{ck}}{2}$  to have continuous transmission, which is half the data rate in the double buffering mode. The reduced data rate can be achieved by reducing the symbol parallelism to half the original parallelism.

Doc. No: ING-IPCTM-FR-v1.0 - 10/07/2018

Pag. 25 / 45

## 3.1.3 Generics

| Generic name       | Туре                                 | Allowed values                                                                                                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------------------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SUPPORTED_MODC ODS | std_logic_<br>vector(26<br>downto 0) | [0x0000001,<br>0x7FFFFFF]                                                                                       | Specifies the ModCods supported by the specific instantiation of the IP core. For each bit, if the bit <i>i</i> is set at '1', the ModCod <i>i</i> +1 is supported.                                                                                                                                                                                                                                                                                 |

| DEFAULT_MODCOD     | integer                              | {1, 2, 3, 4, 5, 6, 7,<br>8, 9, 10, 11, 12,<br>13, 14, 15, 16, 17,<br>18, 19, 20, 21, 22,<br>23, 24, 25, 26, 27} | Set the default ModCod after reset. The corresponding bit in the SUPPORTED_MODCODS generic must be set at '1'                                                                                                                                                                                                                                                                                                                                       |

| BUFFERING_TYPE     | integer                              | {0, 1}                                                                                                          | Specifies the buffering strategy at the CC1 interleaver stages. Set at '1' to select a double buffering strategy, set at '0' to select a single buffering strategy. Double buffering allows higher output data-rate with respect to single buffering, but makes use of more RAM resources.                                                                                                                                                          |

| INPUT_FIFO_SIZE    | integer                              | Integer power of 2's                                                                                            | Specifies the size of the input FIFO in memory locations (32-bit words).                                                                                                                                                                                                                                                                                                                                                                            |

| P_S                | integer                              | {1, 2, 4}                                                                                                       | Specifies the number of symbols produced in parallel at IP-core output. Note that the higher the P_S, the higher the size of the output data signal size                                                                                                                                                                                                                                                                                            |

| P_CC1              | integer                              | {2,4,6,8,12,24}                                                                                                 | Specifies the parallelization degree at the outer encoder (CC1). This parameter depends on the setting of P_S                                                                                                                                                                                                                                                                                                                                       |

| P_CC2              | integer                              | {3,4,5,6,8,10,12,1<br>5,20,24,30,40,60,<br>120}                                                                 | Specifies the parallelization degree at the inner encoder (CC2). This parameter depends on the setting of P_S                                                                                                                                                                                                                                                                                                                                       |

| P_ILV              | integer                              | {2,3,4,5,6,8,10,12,<br>15,20,24,30,40,60<br>}                                                                   | Specifies the parallelization degree at CC1 interleaver. This parameter depends on the setting of P_S                                                                                                                                                                                                                                                                                                                                               |

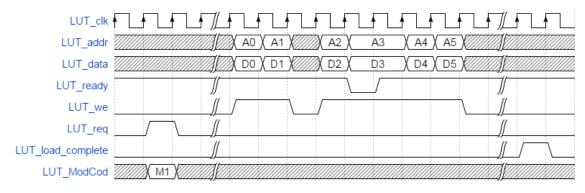

| LOOKUP_TABLES      | integer                              | {0, 1}                                                                                                          | Specifies whether the look-up tables for the implementation of the interleaving and puncturing functions is stored internally or must be loaded from an external non-volatile memory.  Set at '0' to implement lookup tables for interleaver and inner puncturing algorithms within the IP design. Set at '1' to store these values onto an external non-volatile memory and load them during the configuration phase of the telemetry transmitter. |

| SEE_MITIGATION     | integer                              | {0, 1}                                                                                                          | Enables/disables the SEE mitigation techniques in the IP Core. Set at '1' to implement SEE mitigation                                                                                                                                                                                                                                                                                                                                               |

| PILOT_INSERTION    | integer                              | {0, 1}                                                                                                          | Enables/disables the pilot insertion in the PL framing. Set at '1' to implement the Pilot symbol insertion during the transmission of a Physical Frame.                                                                                                                                                                                                                                                                                             |

Doc. No: ING-IPCTM-FR-v1.0 - 10/07/2018

Pag. 26 / 45

| Generic name           | Туре      | Allowed values | Description                                                                                                                                                                                                                                                                                                                               |

|------------------------|-----------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PREDISTORTION_TY<br>PE | integer   | {0, 1}         | Selects the pre-distortion type, which can be OFF (0) or ON (1).  Set at 0 to turn off symbol pre-distortion.  Set at 1 to load pre-distortion parameters in dedicated registers. This solution allows changing the pre-distortion parameters at runtime. Predistortion registers can be initialized at reset through dedicated generics. |

| PREDIST_RING_0_R<br>E  | real      | [-1.2, 1.2]    | Pre-distortion parameter reset value for ModCods from 1 to 12, real part (QPSK and 8PSK modulations). It is used also for Pilot symbols when expected.                                                                                                                                                                                    |

| PREDIST_RING_0_IM      | real      | [-1.2, 1.2]    | Pre-distortion parameter reset value for ModCods from 1 to 12, imaginary part (QPSK and 8PSK modulations). It is used also for Pilot symbols when expected.                                                                                                                                                                               |

| PREDIST_RING_1_R<br>E  | real      | [-1.2, 1.2]    | Pre-distortion parameter reset value for ModCods from 13 to 27, first ring, real part                                                                                                                                                                                                                                                     |

| PREDIST_RING_1_IM      | real      | [-1.2, 1.2]    | Pre-distortion parameter reset value for ModCods from 13 to 27, first ring, imaginary part                                                                                                                                                                                                                                                |

| PREDIST_RING_2_R<br>E  | real      | [-1.2, 1.2]    | Pre-distortion parameter reset value for ModCods from 13 to 27, second ring, real part                                                                                                                                                                                                                                                    |

| PREDIST_RING_2_IM      | real      | [-1.2, 1.2]    | Pre-distortion parameter reset value for ModCods from 13 to 27, second ring, imaginary part                                                                                                                                                                                                                                               |

| PREDIST_RING_3_R<br>E  | real      | [-1.2, 1.2]    | Pre-distortion parameter reset value for ModCods from 18 to 27 third ring, real part                                                                                                                                                                                                                                                      |

| PREDIST_RING_3_IM      | real      | [-1.2, 1.2]    | Pre-distortion parameter reset value for ModCods from 18 to 27 third ring, imaginary part                                                                                                                                                                                                                                                 |

| PREDIST_RING_4_R<br>E  | real      | [-1.2, 1.2]    | Pre-distortion parameter reset value for ModCods from 23 to 27, fourth ring, real part                                                                                                                                                                                                                                                    |

| PREDIST_RING_4_IM      | real      | [-1.2, 1.2]    | Pre-distortion parameter reset value for ModCods 23 to 27, fourth ring, imaginary part                                                                                                                                                                                                                                                    |

| SRRC_ENABLE            | integer   | {0, 1}         | Enables/disables the SRRC filtering. Set at '1' to implement the SRRC filter                                                                                                                                                                                                                                                              |

| SRRC_ROLLOFF           | integer   | {0, 1, 2, 3}   | Specifies the roll-off for the SRRC filter.  '0' means a roll-off of 0.20,  '1' means a roll-off of 0.25,  '2' means a roll-off of 0.30, and  '3' means a roll-off of 0.35                                                                                                                                                                |

| RESET_POLARITY         | std_logic | {'0', '1'}     | Specifies the polarity of the reset signal. '0': Active-low reset '1': Active-high reset                                                                                                                                                                                                                                                  |

| SCRAMBLING_NUMB<br>ER  | integer   | [0, 262142]    | Specifies the scrambling number used for the pseudo-randomizer block.                                                                                                                                                                                                                                                                     |

| CC1_PIPE               | integer   | {0, 1}         | Specifies the presence of the outer encoder output pipeline. Set at '1' to enable the pipeline instantiation.                                                                                                                                                                                                                             |

Doc. No: ING-IPCTM-FR-v1.0 - 10/07/2018

Pag. 27 / 45

| Generic name          | Туре                                | Allowed values     | Description                                                                                                                                                                                                                            |

|-----------------------|-------------------------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ROW2COL_PIPE          | integer                             | {0, 1}             | Specifies the presence of the row2col output pipeline. Set at '1' to enable the pipeline instantiation.                                                                                                                                |

| CC2_PIPE              | integer                             | {0, 1}             | Specifies the presence of the inner encoder output pipeline. Set at '1' to enable the pipeline instantiation.                                                                                                                          |

| PREDISTORTION<br>PIPE | integer                             | {0, 1, 2, 3}       | Specifies the presence of the pre-distortion input/output pipeline registers:  '0': no pipeline stages present '1': output pipeline stage present '2': input pipeline stage present '3': both input and output pipeline stages present |

| SRRC_PIPE             | std_logic_<br>vector(4<br>downto 0) | ["00000", "11111"] | Specifies the presence of SRRC pipelines. The available pipelines are 5                                                                                                                                                                |

Table 3-5 Top-level Generic Map

#### 3.1.4 Ports

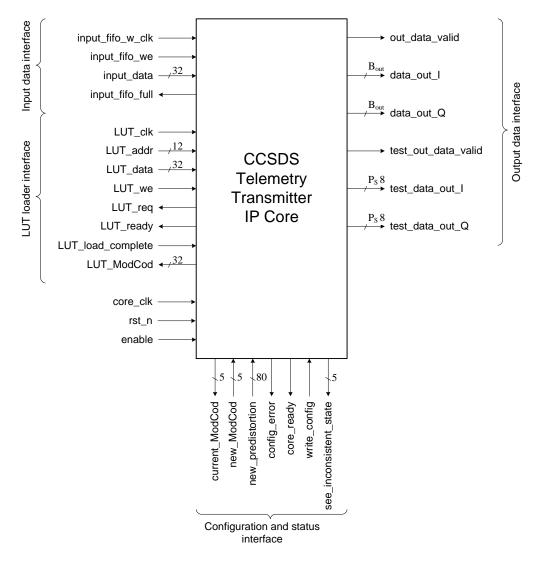

The CCSDS Telemetry Transmitter IP core ports can be divided into the following interfaces, based on the functionality they are related to:

- Input data interface

- Output data interface

- Configuration and status interface

- LUT loader interface

- Clock, reset and enable

Figure 3-6 shows the top-level interfaces of the IP core. The interfaces are detailed in the following sub-sections.

Figure 3-6 CCSDS Telemetry Transmitter IP Core top-level interface

Doc. No: ING-IPCTM-FR-v1.0 - 10/07/2018

Pag. 29 / 45

#### 3.1.4.1 Input data interface

| Port name        | I/O | bits | Clock domain     | Description                                                                                                                                                  |

|------------------|-----|------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| input_fifo_w_clk | I   | 1    | input_fifo_w_clk | Write clock for the input FIFO buffer.                                                                                                                       |

| input_fifo_we    | I   | 1    | input_fifo_w_clk | Write enable for the input FIFO buffer. When this signal is asserted on the rising-edge of input_fifo_w_clk, input_data is written to the input FIFO buffer. |

| input_data       | I   | 32   | input_fifo_w_clk | Data bits to be written to the input FIFO buffer.                                                                                                            |

| input_fifo_full  | 0   | 1    | input_fifo_w_clk | Indicates that the input FIFO buffer is full and every write operation is ignored.                                                                           |

Table 3-6 Input data interface

The input data interface provides the means to feed data to the IP core for processing. The IP core has an asynchronous input buffer to overcome problems due to clock domain crossing when integrating the IP core in the system. The input data interface is made of a 32-bit data bus <code>input\_data</code>, with simple write\_enable/full control signals (<code>input\_fifo\_we</code>, <code>input\_fifo\_full</code>). The interface is synchronous to <code>input\_fifo\_w\_clk</code>. When <code>input\_fifo\_full</code> is asserted, write operations are ignored, to avoid overwriting FIFO contents.

Figure 3-7 Input data interface timing

Pag. 30 / 45

#### 3.1.4.2 Output data interface

| Port name         | I/O | bits   | Clock domain | Description                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|-------------------|-----|--------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| out_data_valid    | 0   | 1      | core_clk     | Indicates that data_out_I and data_out_Q outputs are valid.                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |